ZHCAAR2 May 2021 LMP2012QML-SP , LMP7704-SP , TPS7A4501-SP

设计步骤

想了解对所需规格的电阻值进行计算的Excel计算器,请参阅设计参考资料。

- 定义电路的输入电压范围。本设计中,选择 Vin_min = 0V,Vin_max = 5V。

- 定义电路的输出电流范围。本设计中,选择 Iout_min = 4mA,Iout_max = 20mA。

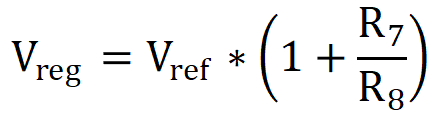

- 计算 R7 和 R8 以设置 TPS7A4501-SP LDO 的输出电压。可调 LDO 的输出电压的设置公式如下:

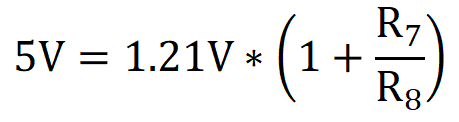

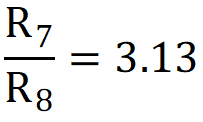

在这个公式中,Vref 是 LDO 的内部带隙基准电压。TPS7A4501-SP 的标称基准电压 Vref = 1.21V,而本设计的目标是 Vreg = 5V,适用如下:

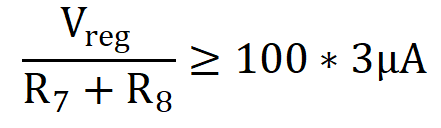

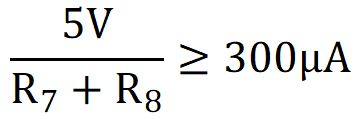

在选择值时,遵循以下指导原则:从 LDO 输出端到接地端的反馈电阻器中的电流必须至少是进入 ADJ 引脚的漏电流的 100 倍,以避免出现输出精度问题。对于 TPS7A4501-SP,ADJ 引脚的漏电流为 3μA(典型值)。由此产生以下不等式:

16.67kΩ ≥ R7 + R8

16.67kΩ ≥ R7 + R8with R8 = 3.97kΩ (标准值),下述等式成立:

R7 = 3.97kΩ * 3.13 = 12,426Ω ≈ 12.4kΩ (标准值)有了 R7 和 R8 的这些值,下述等式有效:

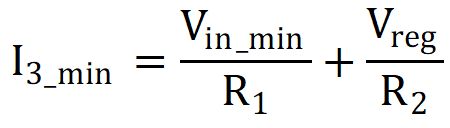

R7 + R8 = 3.97kΩ + 12.4kΩ = 16.37kΩ ≤ 16.67kΩ注: 由于本设计具有电流预算限制,因此最好将 R7 和 R8 的大小设置为接近该限制,以最小化此静态电流贡献。 - 定义流经 R3 的最小和最大电流。在定义这些电流之前,请参阅设计注意事项 5。本设计中,选择 I3_min = 20μA,I3_max = 100μA。

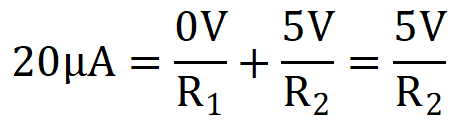

- 如设计步骤 4所定义的,计算 R1 和 R2 的值以设置 I3_min 和 I3_max。为此,请使用第一个公式以及 Vreg、Vin_min、Vin_max、I3_min 和 I3_max 的技术参数。当 Vin = Vin_min 时,得到以下等式:

R2 = 250kΩ (标准值)

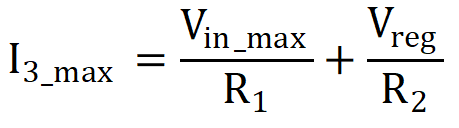

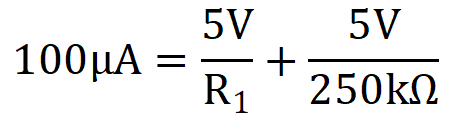

R2 = 250kΩ (标准值)当 Vin = Vin_max 时,以下等式成立:

R1 = 62.5kΩ ≈ 62kΩ (标准值)

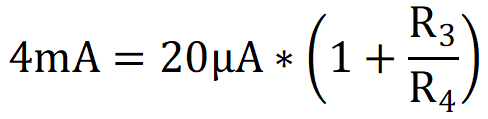

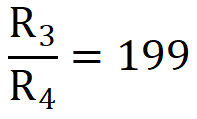

R1 = 62.5kΩ ≈ 62kΩ (标准值) - 计算 R3 / R4 以设置所需的电流增益。为此,请使用该公式以及 Iout_min 和 I3_min。

- 选择 R3 和 R4 的值。对R3大小的调整远没有对 R4 大小的调整重要得多,因为在对 R3 进行大小调整时容易粗心导致裕量问题。要了解原因,请分析最大负载条件 (Iout = Iout_max = 20mA) 下的节点电压。负载电压如下:Vload = Iout_max * Rload = 20mA × 250Ω = 5V

大部分输出电流会通过 R4,因此当 R4 = 100Ω 时,Iret 处的电压约为:

5V + 100Ω * 20mA = 7V

Vreg 以 Iret 为基准,因此相对于电源接地,Vreg = 7V + 5V = 12V,在这种情况下,LDO 进入压降。如果 LDO 进入压降,LDO 将失去其电源抑制 (PSR) 特性,并且运算放大器的正电源电压降低,因此其驱动晶体管基极以提供额外输出电流的能力也会降低。此外,如果 Vreg 下降,则流经 R3 的电流将减小,电路开始表现出非线性行为。另外,如果 R6 太大,则 R6 上的额外电压降会进一步降低晶体管的可用裕量。

考虑到这些因素,选择 R4 = 50Ω 以避免裕量问题。因此:

R3 = 199 * 50Ω = 9.95kΩ ≈ 9.88kΩ (标准值