ZHCAAX3 March 2021 TMS320F280021 , TMS320F280021-Q1 , TMS320F280023 , TMS320F280023-Q1 , TMS320F280023C , TMS320F280025 , TMS320F280025-Q1 , TMS320F280025C , TMS320F280025C-Q1 , TMS320F280040-Q1 , TMS320F280040C-Q1 , TMS320F280041 , TMS320F280041-Q1 , TMS320F280041C , TMS320F280041C-Q1 , TMS320F280045 , TMS320F280048-Q1 , TMS320F280048C-Q1 , TMS320F280049 , TMS320F280049-Q1 , TMS320F280049C , TMS320F280049C-Q1 , TMS320F28075 , TMS320F28075-Q1 , TMS320F28076 , TMS320F28374D , TMS320F28374S , TMS320F28375D , TMS320F28375S , TMS320F28375S-Q1 , TMS320F28376D , TMS320F28376S , TMS320F28377D , TMS320F28377D-EP , TMS320F28377D-Q1 , TMS320F28377S , TMS320F28377S-Q1 , TMS320F28378D , TMS320F28378S , TMS320F28379D , TMS320F28379D-Q1 , TMS320F28379S , TMS320F28384D , TMS320F28384D-Q1 , TMS320F28384S , TMS320F28384S-Q1 , TMS320F28386D , TMS320F28386D-Q1 , TMS320F28386S , TMS320F28386S-Q1 , TMS320F28388D , TMS320F28388S , TMS320F28P650DH , TMS320F28P650DK , TMS320F28P650SH , TMS320F28P650SK , TMS320F28P659DH-Q1 , TMS320F28P659DK-Q1 , TMS320F28P659SH-Q1

3 基于 4 类 PWM 的 PFC CRM/ZVS 实现

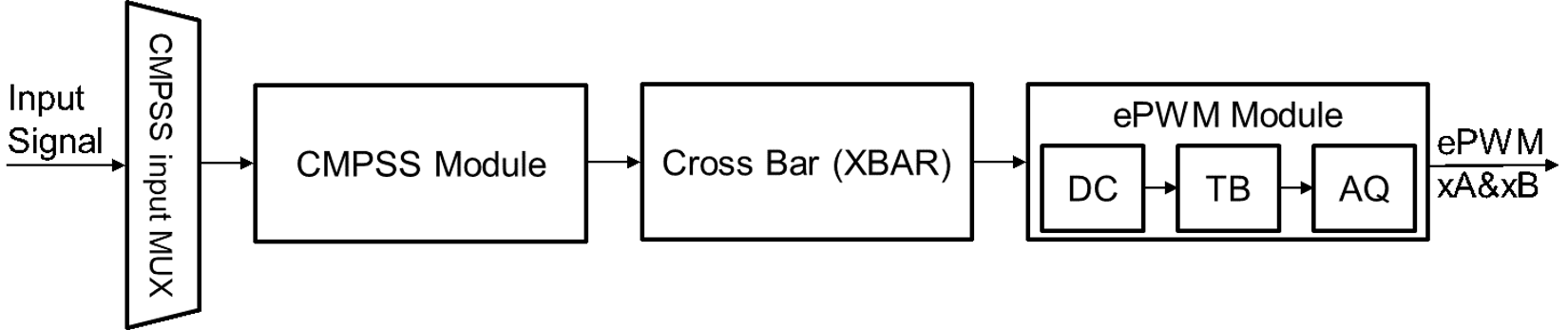

图 3-1 显示从外部 PFC 功率级硬件到 C2000 内部外设的信号接口,该接口用于生成 PWM 信号。本报告以 CMPSS5、X-BAR(TRIP5)、ePWM1 为例介绍了通过 4 类 PWM 实现 CRM/ZVS PFC 的过程。

图 3-1 信号流程图

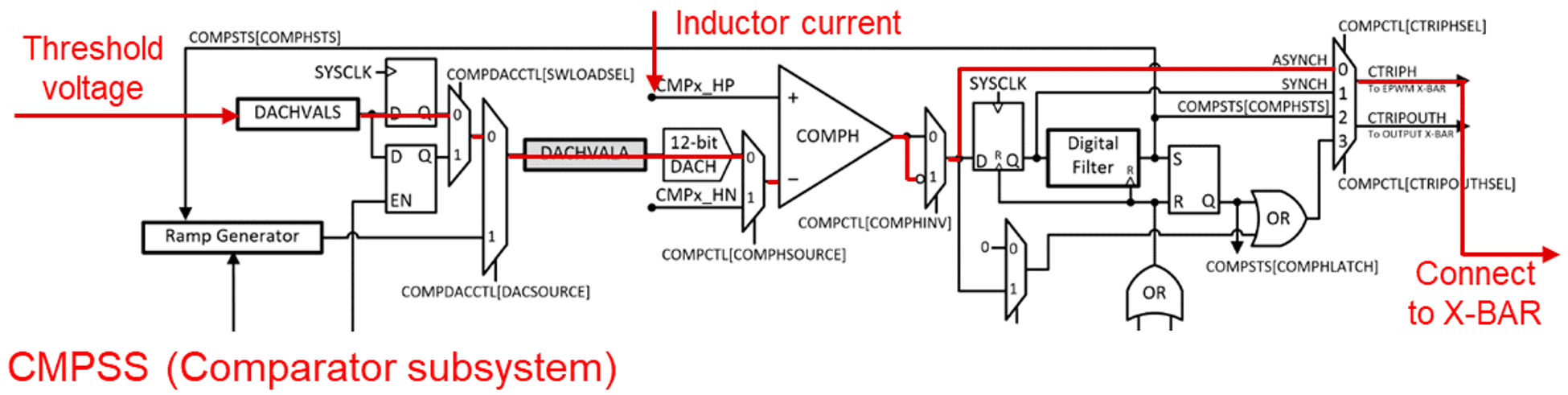

图 3-1 信号流程图图 3-1 中的输入信号是 PFC 电感器电流 iL。选择此信号作为 CMPSS 模块的 COMPH 正极引脚的输入,详情参见图 3-2。捕捉电流过零 (ZC) 的阈值是接近零的固定值,应用于 DACHVALS(阴影寄存器 DAC 值)。电流 ZC 阈值通过参考 DAC 设置为 COMPH 的负输入。选择比较器的反相输出作为 CTRIPH 并异步连接到 X-BAR。

图 3-2 C2000 MCU CMPSS 方框图

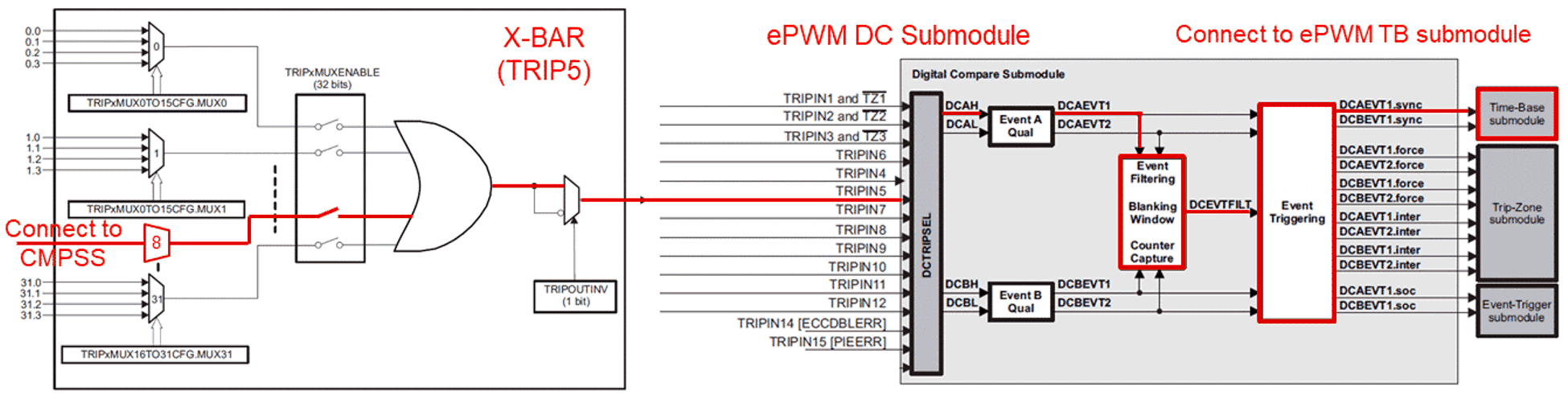

图 3-2 C2000 MCU CMPSS 方框图CMPSS5 CTRIPH 信号连接到 X-BAR TRIP5 mux8,如图 3-3 中所示。若要使任何信号直达 ePWM,请启用 TRIP5MUXENABLE 寄存器中的 mux8。CMPSS 输出通过 ePWM X-BAR 输送到 ePWM 直流子模块。TRIP5 指电感器电流负过零 (NZC) 事件,通过设置 DCAHTRIPSEL 生成 DCAH 信号。请注意,正过零事件是按消隐窗口过滤的,如图 3-7 所示。然后,TZDCSEL 寄存器的配置限定对选定 DCAH 信号的操作,该信号生成 DCAEVT1 事件。然后,通过配置 DCACTL 过滤 DCAEVT1 事件以提供有过滤版本的事件信号的 DCAEVT1.sync。然后 DCAEVT1.sync 生成一个同步脉冲,发给时基计数器。

图 3-3 X-BAR 和 ePWM 直流模块接口

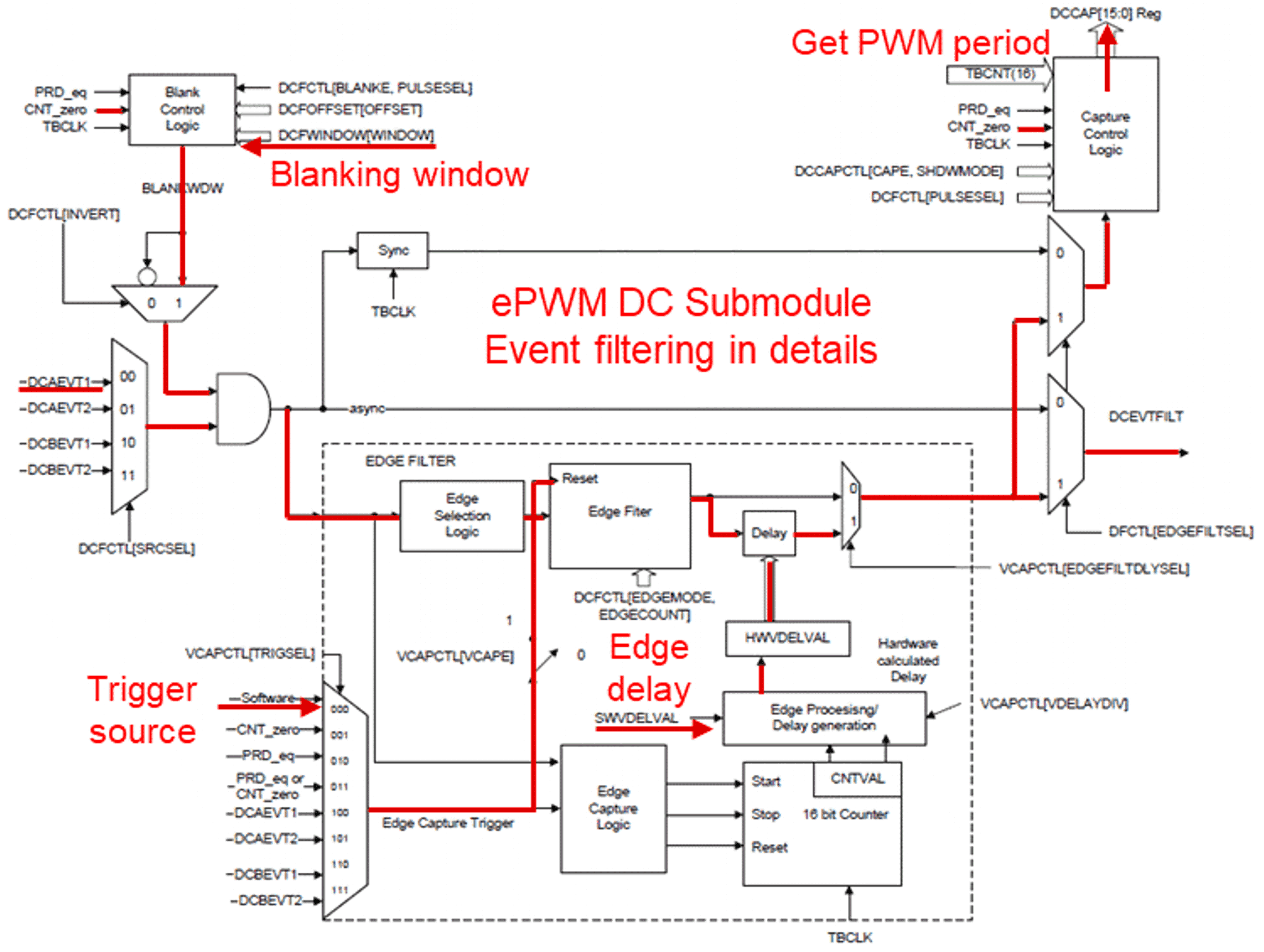

图 3-3 X-BAR 和 ePWM 直流模块接口图 3-4 详细展示了事件过滤逻辑块,这对于实现 ZVS/ZCS 至关重要。事件过滤块可捕捉跳闸事件的 TBCTR 值以提供有 PWM 周期的控制算法并将周期值存储在 DCCAP 寄存器。消隐逻辑用于在生成正确的同步信号前筛除信号上的潜在噪声和电感器电流正过零 (PZC) 事件。图 3-4 所示为事件过滤逻辑模块中的信号流。选择 DCAEVT1 事件作为带有消隐窗口(消隐控制逻辑)的事件过滤逻辑块 (DCFCTL[SRCSEL]) 的输入。这时,比较器输出被选为事件过滤逻辑块的输入。消隐窗口与 DCAEVT1 进行与运算。选择软件触发源作为重置并重新启动边沿滤波器 (VCAPCTL[TRIGSEL]) 的事件。最后,根据硬件参数配置 VCAPCTL [EDGEFILTDLYSEL] 以应用延迟(SWVDELVAL 中的软件编程值)。现在,DCCAP 可以捕捉与电感器电流负过零相关的事件的 TBCTR 值。该 TBCTR 值表示当前 PWM 开关循环的周期。

图 3-4 直流子模块中的边沿滤波器和捕捉控制逻辑

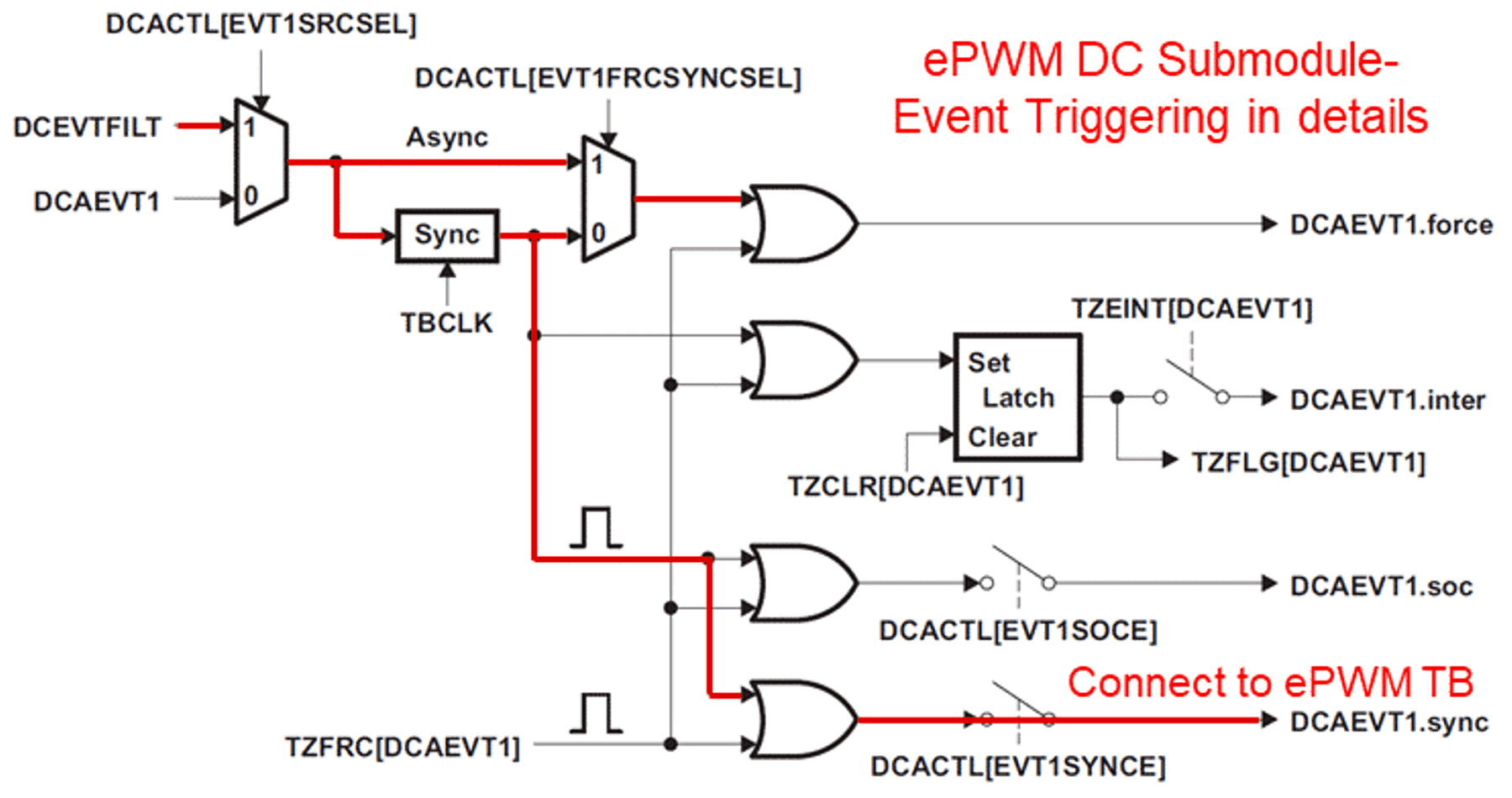

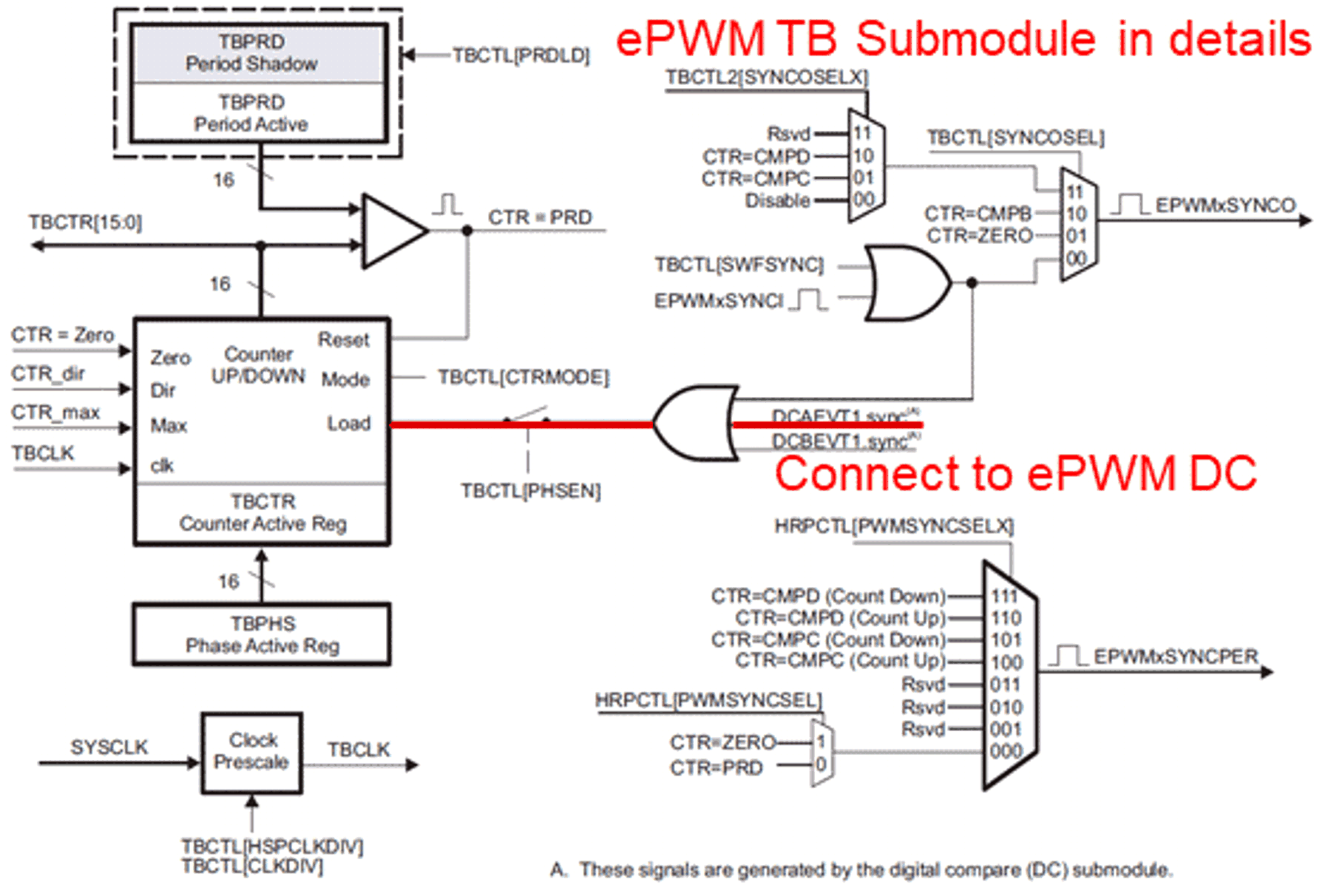

图 3-4 直流子模块中的边沿滤波器和捕捉控制逻辑最后,通过设置事件触发块的 DCACTL[EVT1SYNCE] 启用 DCAEVT1.sync(如图 3-5 中所示),并通过设置时基子模块的 TBCTL[PHSEN] 启用相移以同步 TBCTR(如图 3-6 中所示)。

图 3-5 CRM/ZVS PFC 中使用的事件触发块

图 3-5 CRM/ZVS PFC 中使用的事件触发块 图 3-6 CRM/ZVS PFC 中使用的时基子模块

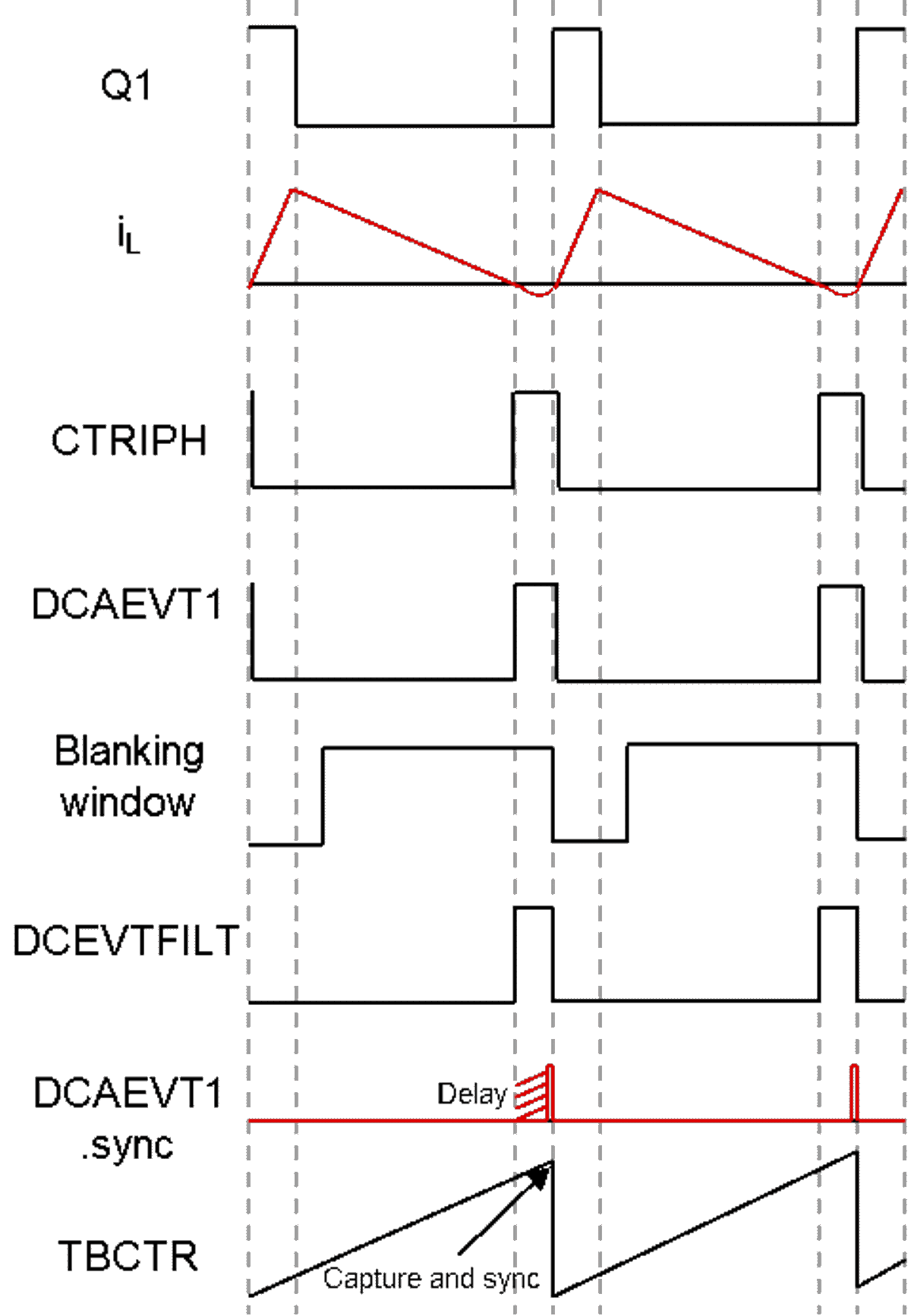

图 3-6 CRM/ZVS PFC 中使用的时基子模块图 3-7 显示外设配置后的主要信号波形。DCAEVT1 信号的上升沿和下降沿代表基于图 3-7 的相应正负过零点。消隐窗口与 DCAEVT1 进行与运算,以生成 DCEVTFILT,以便在 MOSFET 导通时间内筛除电感器电流正过零 (PZC) 边沿和噪声。这样,消隐窗口长度应该比 PWM 导通时间长。直流子模块应用对应电感器负过零 (NZC) 边沿的延迟来生成同步事件。

图 3-7 CRM PFC 4 类 PWM 实施中的信号波形

图 3-7 CRM PFC 4 类 PWM 实施中的信号波形