ZHCAB56A January 2021 – February 2022 BQ769142 , BQ76942 , BQ76952

8 低侧 FET 的预充电和预放电

BQ769x2 的 DDSG 和 DCHG 输出结合了前置和主 FET 驱动信号。如果设计人员想要添加预充电和/或预放电功能,可以选择从主机控制预充电或预放电路径,或者使用逻辑在应用前置信号时抑制主 FET 驱动器。使用主机时,预充电和预放电 FET 驱动器可能看起来像前面部分中说明的主 FET 驱动器。

BQ769x2 的预充电和预放电输出仅以 BAT 电压为基准,以 VSS 为基准的数字版本不可用。若要在低侧设计中添加预充电和预放电功能,需要通过一个电路进行从高侧到低侧 FET 的电压转换,示例参见图 8-1。P 沟道信号 FET(Q28、Q29)用于生成电流,电流将流向低侧的电阻(R51、R52)以导通 FET。齐纳二极管(D8、D9)限制了 FET 栅极的接入电压。漏极路径中的电阻(R58、R60)降低了 Zener 二极管的接入电压,限制了漏极电流。如有需要,可使用拉电流路径中的电阻来限制电流。电流将因电池电压而异。电阻的比率将决定低侧 FET 栅极的电压。也必须调整较低电阻的大小以执行关断。PACK- 可以摆动到 GND 之下和 PACK+ 之上,因此可加入二极管 (D7) 以避免电流经过这些器件。

图 8-1 中的电路显示信号转换电路以及预充电和预放电 FET,通过 4.7kΩ 电阻限制预充电和预放电的电流路径。此系统解决方案并不完整,因为它不含在主 FET 未同时导通时让这些电路工作的逻辑。例如,仅当 DDSG 激活并且 PDSGgate 信号处于低电平时,才会启用主放电 FET。4.7kΩ 电阻也需要调整,以实现设计中所需的电流和允许的功率。

PDSG 和 PCHG 在关断时具有高阻抗,PDSG 由 R55 和 R57 上拉,PCHG 由 R56 和 R59 上拉。当 PDSG 和 PCHG 激活时,电压拉至 BAT 电平以下,适当时导通 Q28 和 Q29。连接示波器探头以观察 PDSG 和 PCHG,这一般会下拉信号并导通 FET,因此图中没有显示这些信号。

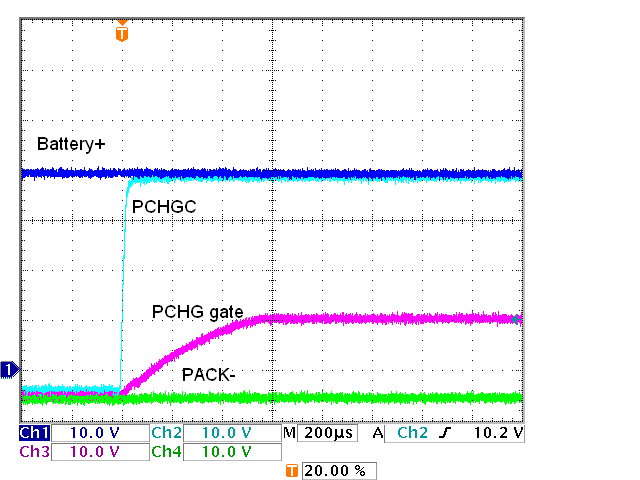

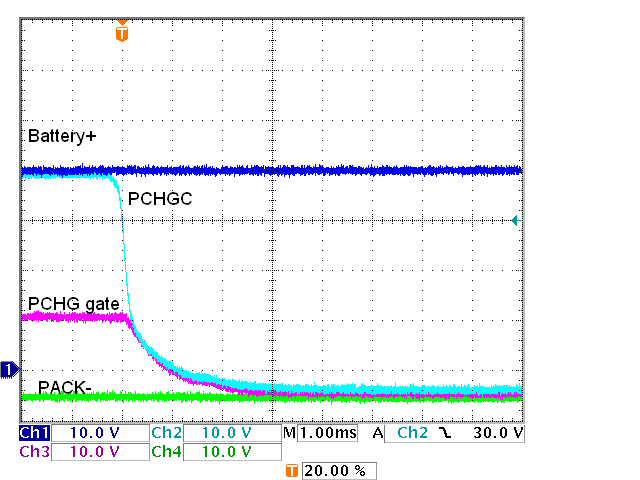

有关预充电电路的图 8-2 和图 8-3 展示了电平转换电路的基本操作。在此电路中,电平转换直接控制 FET。在这些波形中,DCHG 断开连接,所以主充电 FET 保持关断,PACK- 保持在 GND 之下。示波器探头的加载将下拉高阻抗输出,导通外部 FET,因此波形中没有显示 PCHG 信号。当 CHG 信号变为低电平时,P 沟道 FET 将 PCHGC 信号上拉至电池电压,将 PCHG 栅极信号提升至齐纳二极管的限值。由于路径的电流受限,充电器电压保持在电池电压(图中的探头基准)之下。用大电阻保持小电流,所以开关缓慢,关断时最为明显。由于路径中的电流减小,缓慢开关可能适合 FET,但经常因低电流而使用小型 FET。使用合适的方法进行设计。生成逻辑电平信号来控制主充电驱动器时,请注意开关速度以及 PACK- 的大幅电压波动。使用以 VSS 为基准的路径进行逻辑控制。另外,当考虑使用此电路时,注意 PCHG 和 PDSG 以 BQ769x2 的滤波 BAT 引脚为基准。如果 BAT+ 上存在瞬态,请考虑对 Q28 和 Q29 的 VGS 电压进行滤波或限制,并考虑干扰对逻辑电路的影响。

图 8-2 预充电导通

图 8-2 预充电导通 图 8-3 预充电关断

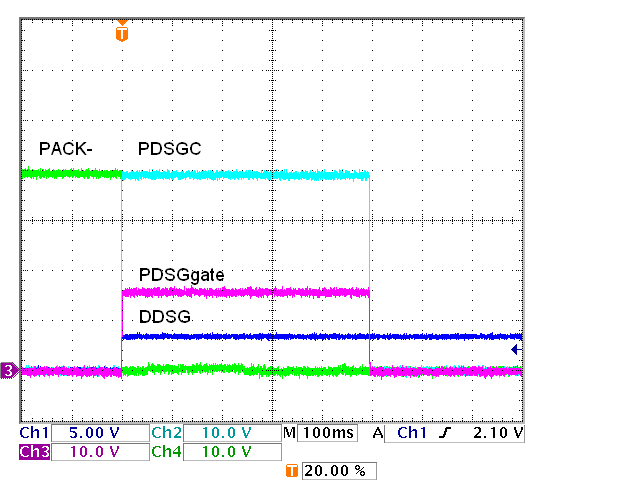

图 8-3 预充电关断图 8-1 中所示的预放电路径以检测电阻为基准,后者不会远离 VSS 并通过 FET 栅极阈值进行调节。图 8-4 展示了在没有主放电 FET 的逻辑控制的情况下测试电路的局限性。PDSG 导通 PDSGC 信号,后者导通 PDSGgate 和预放电路径,但 DDSG 也会变为高电平,从而导通主放电 FET,立即下拉 PACK-,而非使用电流受限的预放电路径。低电平下 PACK- 的电平变化源于预放电周期中 DCHG 信号的临时关断。在预放电期间,需要通过逻辑禁用主放电 FET,以使预放电生效。

图 8-4 预放电导通

图 8-4 预放电导通