ZHCAB56A January 2021 – February 2022 BQ769142 , BQ76942 , BQ76952

5 FET 驱动器设计

IC FET 驱动器将通过合适的输出级,将逻辑电平信号转换为适当的栅极驱动电平。图 5-1 中的设计使用 UCC27524 双路同相 FET 驱动器。一个驱动器用于导通和关断放电 FET,另一个则用于导通充电 FET。充电 FET 的关断由 RGS 或栅极电路实现。UCC27524 是功能强大的驱动器,能够在开关稳压器或其他应用中非常快速地开关栅极。作为这里的负载开关,它需要串联电阻来减慢栅极开关速度,以避免在过流或短路保护等高电流事件关断过程中产生较大电感响应。U2 是此测试中使用的线性稳压器,在电池短路期间由 D12 阻止它放电,而输入通过 R68 及其输入电容器进行滤波。在应用中可使用另一个合适的源(如果可用)。图 5-2 中显示了一个包含四个放电和充电 FET 的电路。电路配置与逻辑电平 FET 电路非常相似,但二极管 D3 是传统的二极管,因为从驱动器可得到更多电压。本应用报告中采用高压驱动方案的测试电路使用 CSD19536KCS FET。

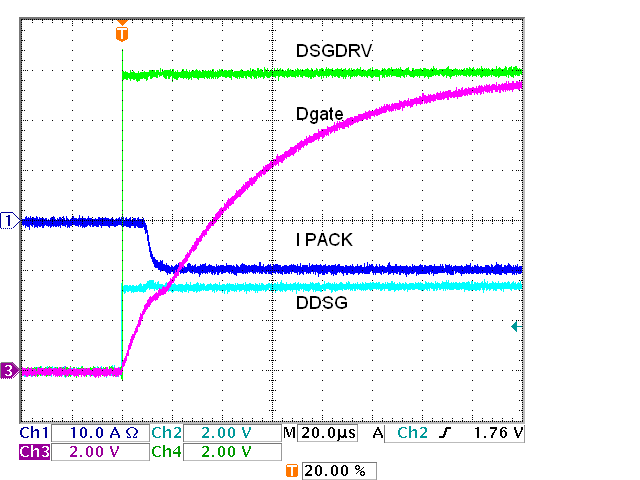

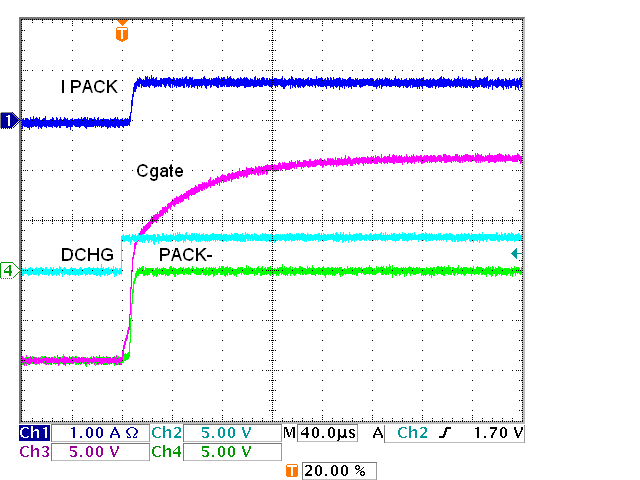

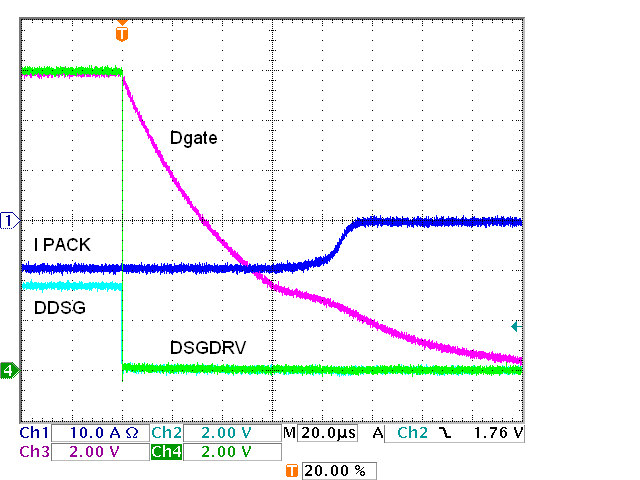

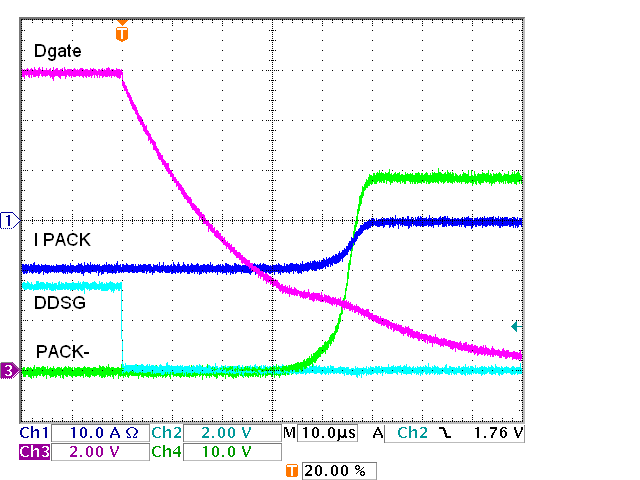

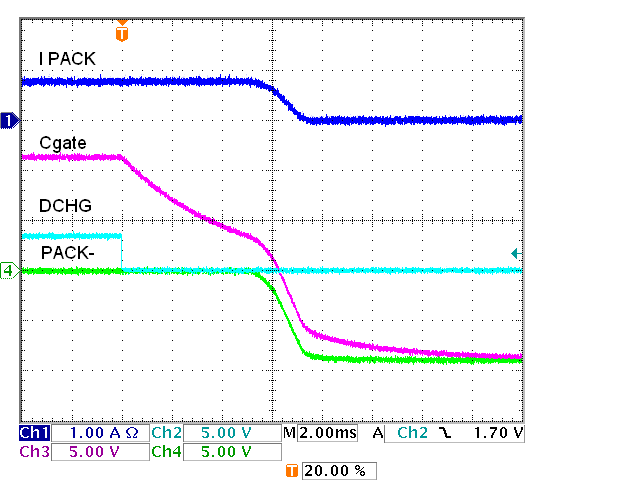

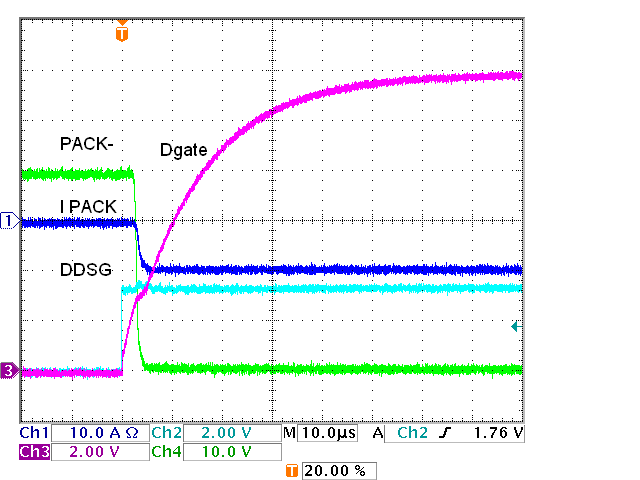

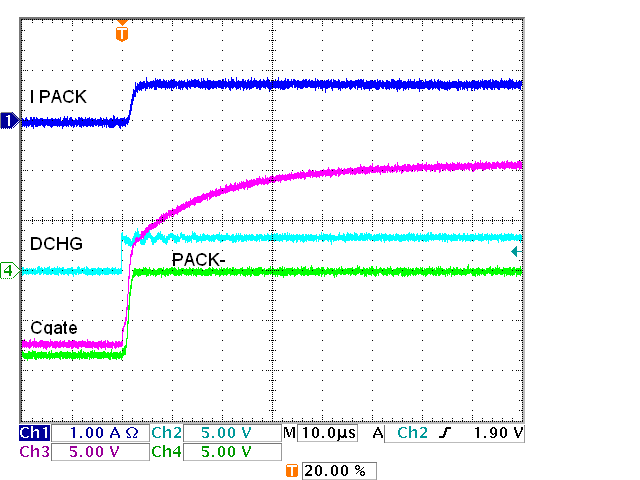

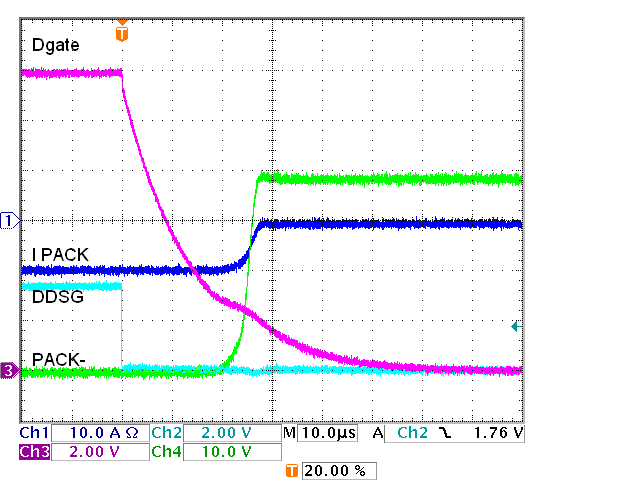

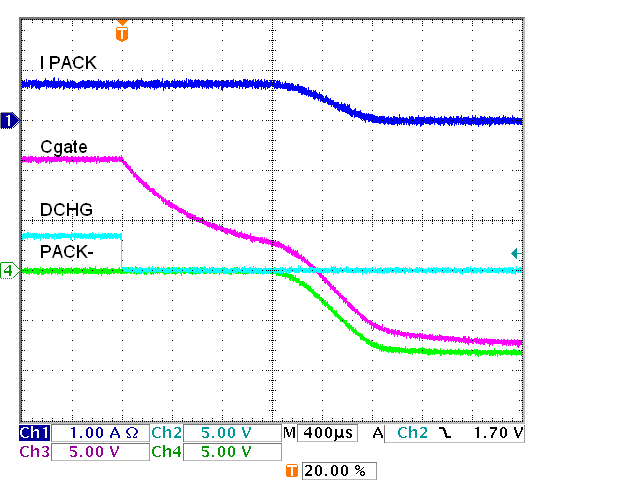

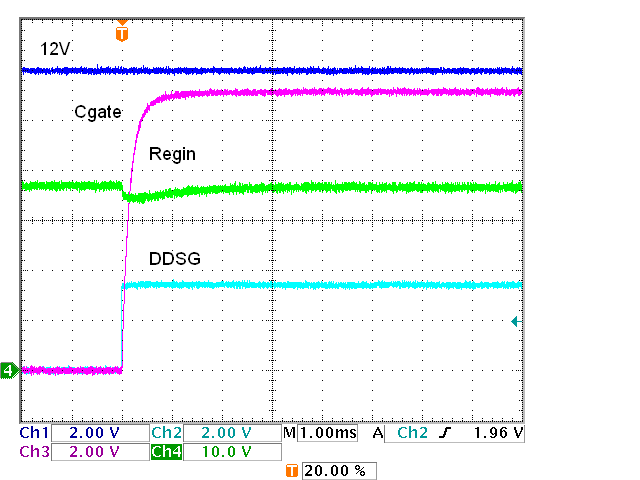

图 5-3 和图 5-4 展示了驱动器的强大响应,以及在没有图 5-2 中的 D6 和 R28 的情况下放电 FET 的开关。串联电阻对栅极和栅极电容的 R-C 响应会减缓栅极电压。FET 的阈值电压更接近 GND 而非驱动电平,因此请注意 DSGDRV 信号下降与电流转换之间的延迟。添加 D6 和 R28 不会改变导通状态(详情如图 5-5 中所示),但会加速关断(如图 5-6 中所示)。可调整 R28 值以加快关断速度。充电 FET 的开关如图 5-7 和图 5-8 中所示。

图 5-3 IC FET 驱动器驱动四个放电 FET 导通

图 5-3 IC FET 驱动器驱动四个放电 FET 导通 图 5-5 IC FET 驱动器驱动四个放电 FET 导通(添加肖特基二极管)

图 5-5 IC FET 驱动器驱动四个放电 FET 导通(添加肖特基二极管) 图 5-7 IC FET 驱动器驱动四个充电 FET 导通

图 5-7 IC FET 驱动器驱动四个充电 FET 导通 图 5-4 IC FET 驱动器驱动四个放电 FET 关断

图 5-4 IC FET 驱动器驱动四个放电 FET 关断 图 5-6 IC FET 驱动器驱动四个放电 FET 关断(添加肖特基二极管)

图 5-6 IC FET 驱动器驱动四个放电 FET 关断(添加肖特基二极管) 图 5-8 IC FET 驱动器驱动四个充电 FET 关断,91kΩ

图 5-8 IC FET 驱动器驱动四个充电 FET 关断,91kΩ图 5-9 中显示了一个包含 12 个放电和充电 FET 的电路设计。12 个 FET 使得栅极的总电容更大。对于 DSG,使用了较小的电阻。R29 等单独的栅极电阻不再只占栅极总电阻的一小部分,所以用铁氧体磁珠替代它们可能较为合适,但测试使用了 51Ω 电阻。在充电路径中,添加了 PNP 晶体管来辅助关断,以避免小电阻在 CHG 导通期间发生偏置。结果如图 5-10 和后续图中所示。请注意,在 PNP 关断电路中,即使 FET 较多,图 5-13 中充电 FET 的关断时间也早于图 5-8 中仅使用下拉电阻时的关断时间。可使用 R24 基极电阻值调整关断速度。

图 5-10 IC FET 驱动器驱动 12 个放电 FET 导通

图 5-10 IC FET 驱动器驱动 12 个放电 FET 导通 图 5-12 IC FET 驱动器驱动 12 个充电 FET 导通

图 5-12 IC FET 驱动器驱动 12 个充电 FET 导通 图 5-11 IC FET 驱动器驱动 12 个放电 FET 关断

图 5-11 IC FET 驱动器驱动 12 个放电 FET 关断 图 5-13 IC FET 驱动器驱动 12 个充电 FET 关断

图 5-13 IC FET 驱动器驱动 12 个充电 FET 关断当开关多个 FET 时,务必在开关期间检查电源。图 5-14 展示了 24 个 FET 导通时 12V 稳压器的输出。电流下拉稳压器输入,而稳压器输入会随着时间恢复。稳压器具有足够的余量,因此下降不显著,调节电压保持恒定。

图 5-14 24 个 FET 导通时的 12V 电源

图 5-14 24 个 FET 导通时的 12V 电源