ZHCABE4A July 2021 – April 2022 PCM3120-Q1 , PCM5120-Q1 , PCM6120-Q1 , TLV320ADC3120 , TLV320ADC5120 , TLV320ADC6120

4 输入共模失真

以下各图展示了 CMRR 和 THD+N 在每个容差模式下具有不同输入电平时的性能。这些曲线在 ADC5120EVM-PDK 板上测得,该板配置为使用 AP2700 和高精度函数发生器实现交流耦合输入。从 Audio Precision 中应用 1kHz、-60dBFS 差分输入音调,并将 750Hz 共模音调应用于 AP2700 的参考节点。60dBFS 的差分音调不够大,无法生成其自己的失真产物。750Hz 共模用于轻松区分从共模变化中产生的任何谐波。

参考这些图时,记住输出 dBFS 和输入电压之间的关系很有帮助。以下是计算示例:

2Vrms = 2.8Vpp

100mVpp = 0.05Vp

100mVpp(以 dBFS 为单位)= 20*log(0.05/2.8) = -35dBFS

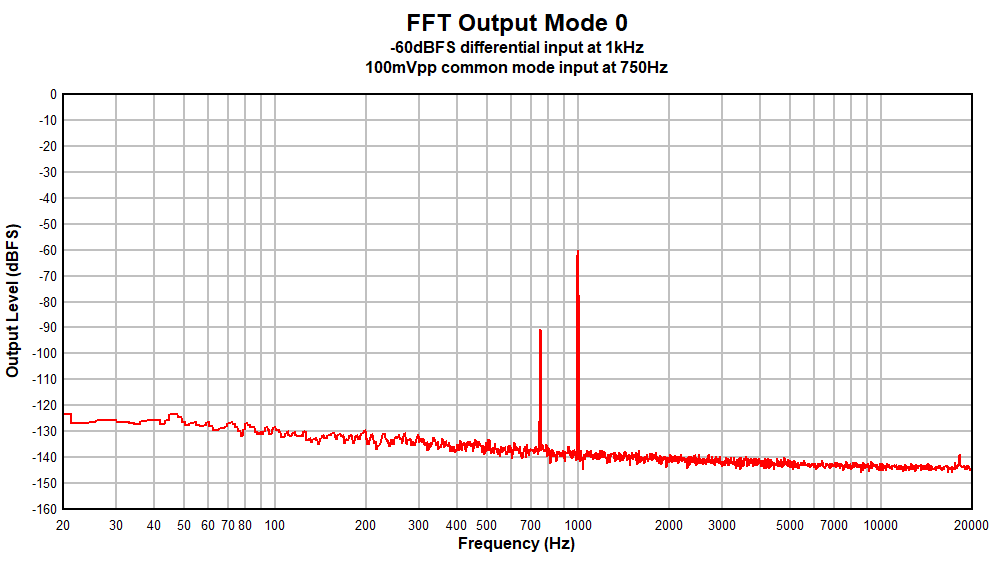

图 4-1 显示了模式 0 下对输入端应用 100mVpp (-35dBFS) 共模音调时的输出频谱。从该图中,我们可以观察到没有发生明显的失真,750Hz 的音调降低了约 (-35dB - (-90dB) = 55dB)。本测试测得的 THD+N 水平为 -93dBFS。

图 4-1 100mVpp 共模下的模式 0 输出 FFT

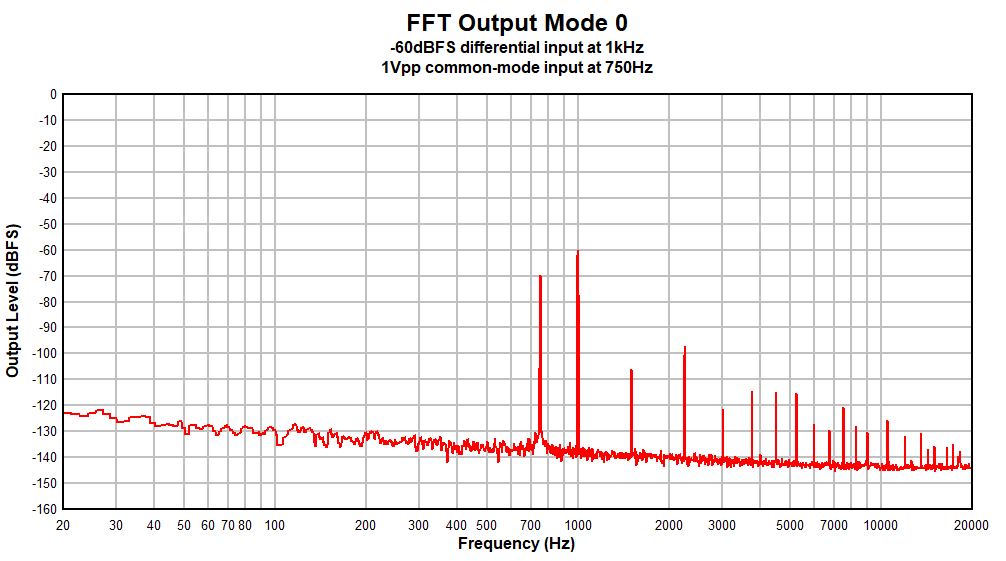

图 4-1 100mVpp 共模下的模式 0 输出 FFT图 4-2 显示了模式 0 下输入共模振幅增加至 1Vpp (-15-dBFS) 时的输出频谱。请注意,这远远超出了模式 0 的最大共模容差,可以如预期的那样看到显著的失真。主 750Hz 音调约为 -70dB,因此 CMRR 仍在 55dB (-15 - (-70) = 55dB) 左右,但 THD+N 水平已降至约 -73dBFS。

图 4-2 1Vpp 共模下的模式 0 输出 FFT

图 4-2 1Vpp 共模下的模式 0 输出 FFT图 4-3 显示了模式 1 下应用于输入的相同 1Vpp 共模信号。模式 1 扩展了支持的共模范围,略微改善了基本 750Hz 音调的共模抑制,并显著降低了从较大的共模信号中引入的失真。

图 4-3 1Vpp 共模下的模式 1 输出 FFT

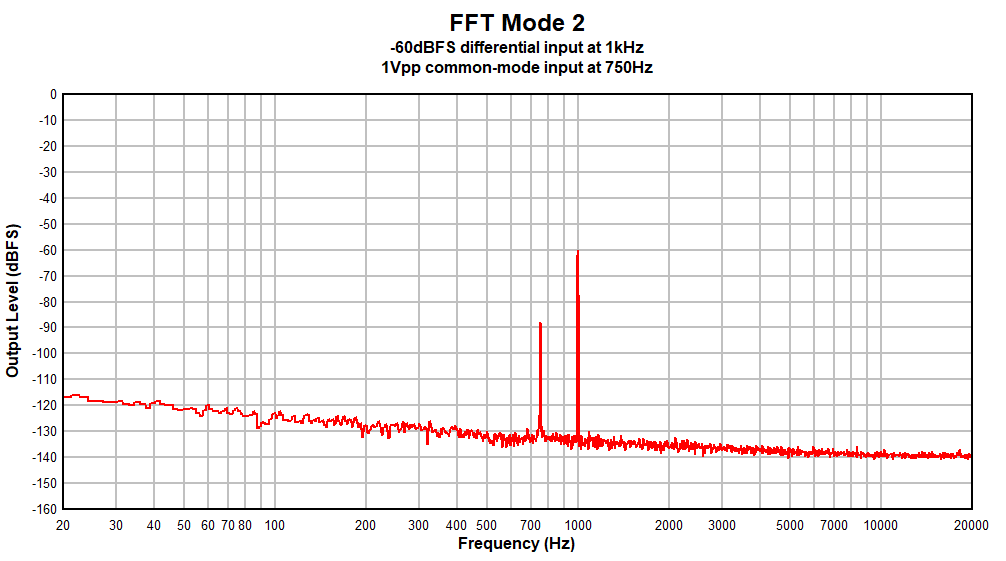

图 4-3 1Vpp 共模下的模式 1 输出 FFT图 4-4 再次显示了模式 2 下应用于输入的相同 1Vpp 共模信号。模式 2 进一步扩展了共模范围,改善了共模抑制,并消除了由较大的输入共模音调产生的失真。

图 4-4 1Vpp 共模下的模式 2 输出 FFT

图 4-4 1Vpp 共模下的模式 2 输出 FFT