ZHCABI3 March 2022 AM2431 , AM2432 , AM2434 , AM6411 , AM6412 , AM6421 , AM6422 , AM6441 , AM6442

- 摘要

- 商标

- 1 系统概述

- 2 硬件必要条件

- 3 硬件配置

- 4 HW 引脚排列、默认跳线和连接

- 5 原理图

- 6 跳线设置和说明

- 7 LED

- 8 软件架构

- 9 驱动和反馈时序

- 10基准测试结果

-

11关于演示的详细用户指南

- 11.1 步骤 0.获取软件并编译

- 11.2 步骤 1.开始使用硬件

- 11.3 步骤 2.配置 ROQ437 EnDat2.2 编码器以缩短 EnDat 2.2 恢复时间(只需在首次使用 ROQ437 编码器时执行一次)

- 11.4 步骤 3.开环 Iq 控制(BUILDLEVEL == OPEN_LOOP_IQ_ID)

- 11.5 步骤 4.闭环 Iq/Id 控制(BUILDLEVEL == CLOSED_LOOP_IQ_ID)

- 11.6 步骤 5.闭环速度控制(BUILDLEVEL == CLOSED_LOOP_SPEED)

- 11.7 步骤 6.闭环位置控制(BUILDLEVEL == CLOSED_LOOP_POSITION)

- 12使用 MCU+SDK 08.00.00.21 & CCS 10.3.1 进行编译

- 13总结

- 14附录 A:详细的电机控制 R5F 处理时间

- 15参考文献

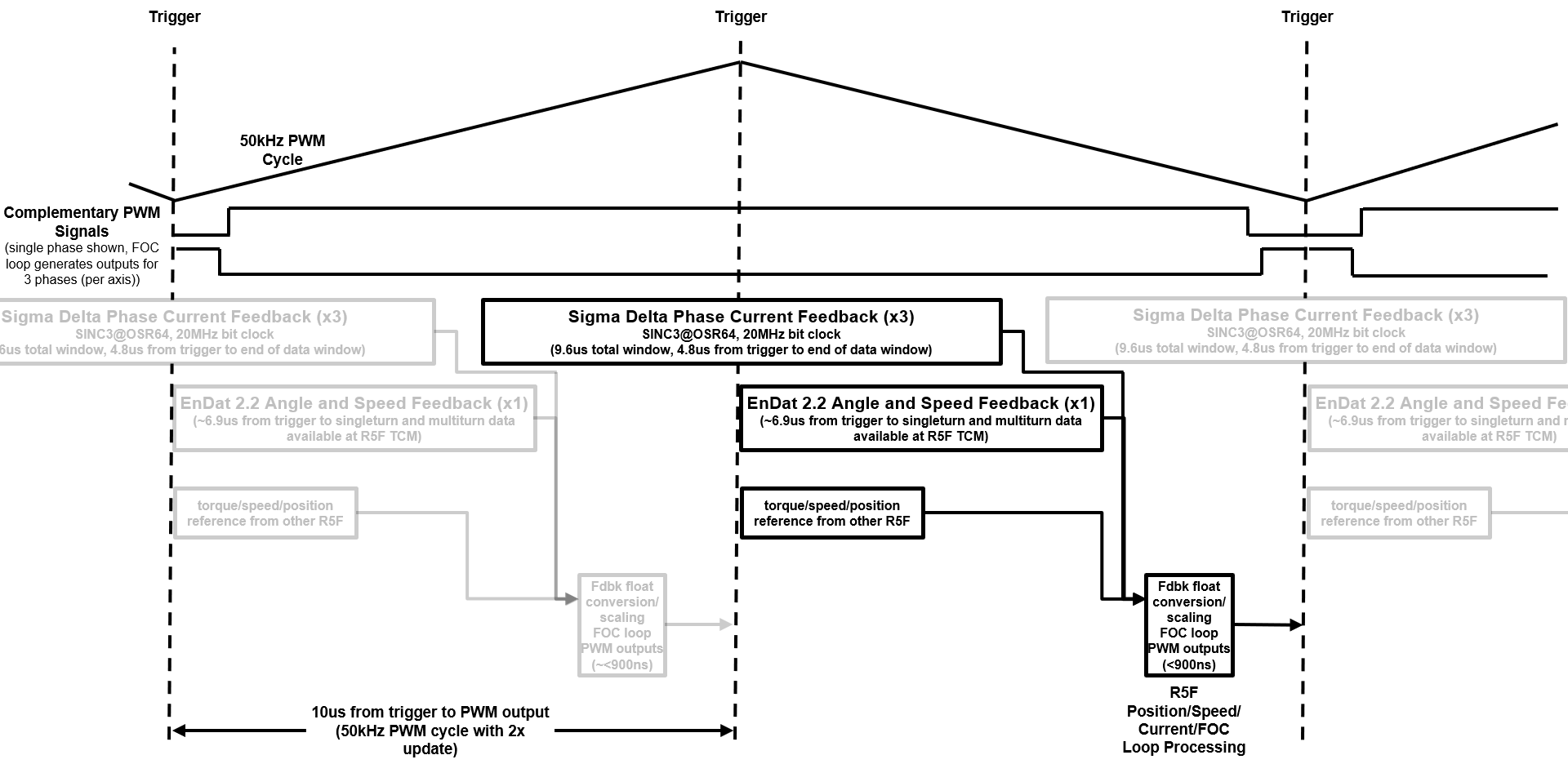

9 驱动和反馈时序

演示中驱动和反馈时序的精度对于正确执行 FOC 环路计算至关重要,进而对整体电机控制性能也至关重要。为了实现目标,此演示设置如下所示:

- 50KHz PWM 周期时间

- 由于 EPWM 外设时钟为 250MHz 而实现了 12 位以上的 PWM 分辨率

- 50KHz/4ns = 5000,这大约等于 12.28 位的分辨率

- 由于 EPWM 外设时钟为 250MHz 而实现了 12 位以上的 PWM 分辨率

- 100KHz FOC 环路更新

- 每个 PWM 周期具有 2 个更新

- 允许在触发点前有 10µs,直到可以捕获反馈,FOC 环路关闭,并且 PWM 值在影子寄存器中更新

- 此处为实现的时序图:

图 9-1 时序图

图 9-1 时序图

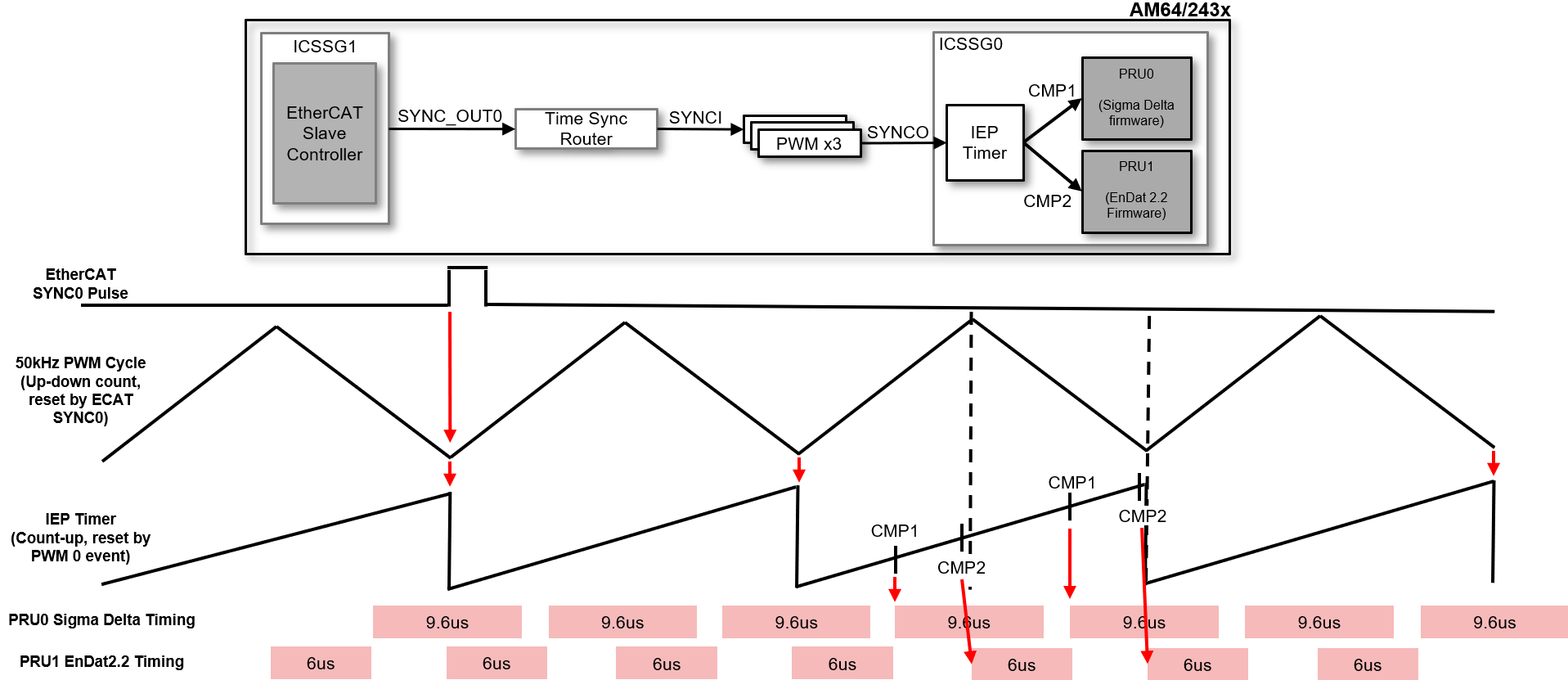

- 适用于 EnDat2.2 和 Σ-Δ 反馈数据的精确触发

- 在 PWM 外设和 ICSSG0 的 IEP 计时器之间使用同步技术,以便在 PWM 周期中的任何时刻精确放置触发器

- EPWM SYNCO 信号可将 IEP 计时器计数器复位,并使用 CMP1 和 CMP2 值触发 EnDat 和 Σ-Δ 的起始点

图 9-2 同步技术

图 9-2 同步技术 - 技术显示在下图中,结果显示在“基准测试结果”部分中