ZHCABL7 March 2022 THVD1406 , THVD1426

2.2 测试二:在低于建议运行条件的情况下发送数据

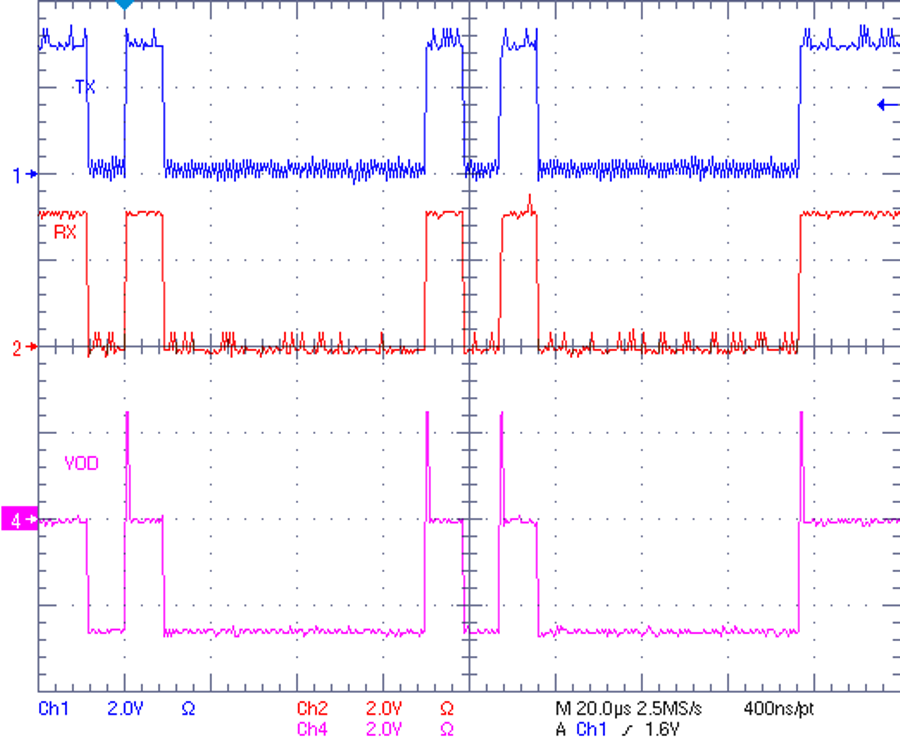

在第二个测试中,硬件设置与测试一完全相同,相同字符串在 115200 的波特率下发送,此波特率大大低于 THVD1426 的建议运行条件 (12 Mbps)。此测试的目的是检查 THVD14x6 能否在低于数据表建议的数据速率下工作。输入数据的 1 位宽度 (8.6-μs) 大大长于驱动器的最大运行时间 (1.45μs)。如上一测试中最后一位的波形所示,差分总线电压在驱动器完成其运行时间(如图 2-3 所示)后变为 0V。因此,每个 1 位输入将在趋稳至 0V 之前在总线上显示尖峰。鉴于接收器阈值 Vth+ 为 -20mV,此 0V 将在接收器输出生成高电平。因此,接收器仍生成正确位。在系统设计中,最好在 A 侧添加一些上拉电阻,在 B 侧添加一些下拉电阻。这些偏置电阻会在空闲总线上生成高于 0V 的恒定电压,以提高抗噪性。有关如何选择电阻值的详细信息,请参阅 RS-485:空闲总线的被动失效防护一文。

图 2-3 低数据速率下 THVD1426 的自动方向控制测试

图 2-3 低数据速率下 THVD1426 的自动方向控制测试