ZHCABM9B May 2022 – November 2023 TPS62860 , TPS62861 , TPS62864 , TPS62866 , TPS62868 , TPS62869 , TPS62870-Q1 , TPS62871-Q1 , TPS62872-Q1 , TPS62873-Q1 , TPS6287B10 , TPS6287B15 , TPS6287B20 , TPS6287B25 , TPSM8287A06 , TPSM8287A10 , TPSM8287A15 , TPSM8287B30

4 运行期间动态输出电压调整

I2C 接口支持在运行期间调整输出电压。通常采用一个或多个 I2C 寄存器设置输出电压,并且可以在运行期间直接重新写入这些寄存器。一些器件还包含 VID 或 VSEL 引脚,用于在两个或更多输出电压之间切换。在这种情况下,仍可以在运行期间根据需要重新写入这些寄存器,也可以对这些寄存器一次写入至特定的工作电压。

例如,LPDDR5 DRAM VDDQ 电源轨可以设置为 0.5V 或 0.3V。通过重写 I²C 寄存器以更改输出电压,或使用 VID 引脚更改为具有不同输出电压的不同 I²C 寄存器,可以实现此电压更改。LPDDR5 DRAM 与前几代相比,提供了额外的节能效果。在空闲状态下,此时 LPDDR5 DRAM 处于低功耗工作状态中,存储器控制器可以使用 LPDDR5 DRAM 的动态电压和频率缩放 VDDQ (DVFSQ) 功能同时降低电源电压和工作频率。

图 4-1 显示了为 LPDDR5 存储器供电的典型方框图,在 VDDQ 电源轨上进行了动态输出电压调整。

图 4-1 TPS62869 为 LPDDR5 DRAM 上的所有电源轨供电,并在 VDDQ 电源轨上进行动态输出电压调整

图 4-1 TPS62869 为 LPDDR5 DRAM 上的所有电源轨供电,并在 VDDQ 电源轨上进行动态输出电压调整系统设计确定是否将使用双电源轨模式来实现额外的节能。与 VDDQ 电源轨(可动态更改)不同,VDD2H/L 始终在固定电压下运行,无论是使用单电源轨还是双电源轨模式。

TPS62869 提供不同的电压斜坡速度,使系统工程师能够为 DVFSQ 由低电平到高电平转换选择正确的条件。例如,如果在 VDDQ 恢复到 0.5V 标称水平,以进行高速运行时需要快速响应,TPS62869 可以将其电压斜坡速度从 1mV/us 调整到 20mV/us。

表 4-1 显示 DVFSQ 转换的最大 VDDQ 斜坡速率。

| VDDQ 压摆率 | 最大值 | 单位 |

|---|---|---|

| 快速响应模式 (大电流) | 20 | mV/us |

| 正常运行 (默认) | 4,8 | mV/us |

此外,可以启用操作参数(例如输出电压变化期间的强制 PWM 模式),以满足 VDDQ 由低电平到高电平转换期间的严格定时要求。这样可在较低的工作状态下进行快速转换,并可防止输出级的缓慢放电,以限制低负载条件下的电压斜坡速度。

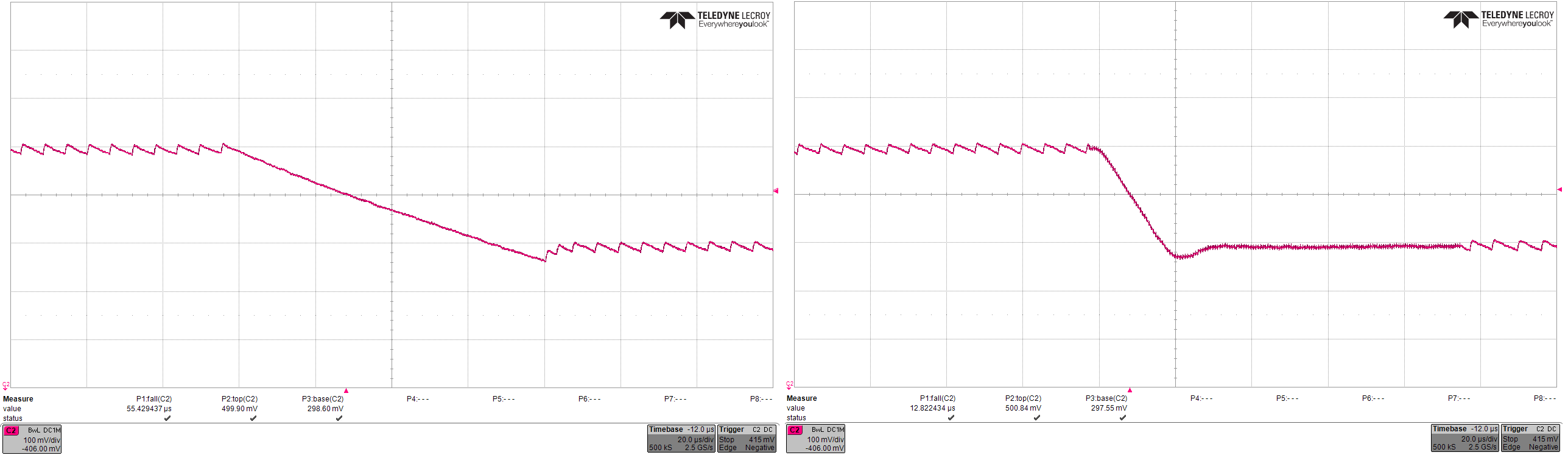

图 4-2 显示了在 100mA 负载条件下输出电压变化期间,采用和不采用强制 PWM 模式时的 0.5V 至 0.3V 转换示例。

图 4-2 20mV/us 压摆率下的 0.5V 至 0.3V 输出转换,IOUT = 100mA,在启用更改期间不采用 FPWM 模式(左)和采用 FPWM 模式(右)

图 4-2 20mV/us 压摆率下的 0.5V 至 0.3V 输出转换,IOUT = 100mA,在启用更改期间不采用 FPWM 模式(左)和采用 FPWM 模式(右)