ZHCAC48 February 2023 TLC6C5748-Q1

2.2.2.2 3.3V I/O 电压,而非 5V

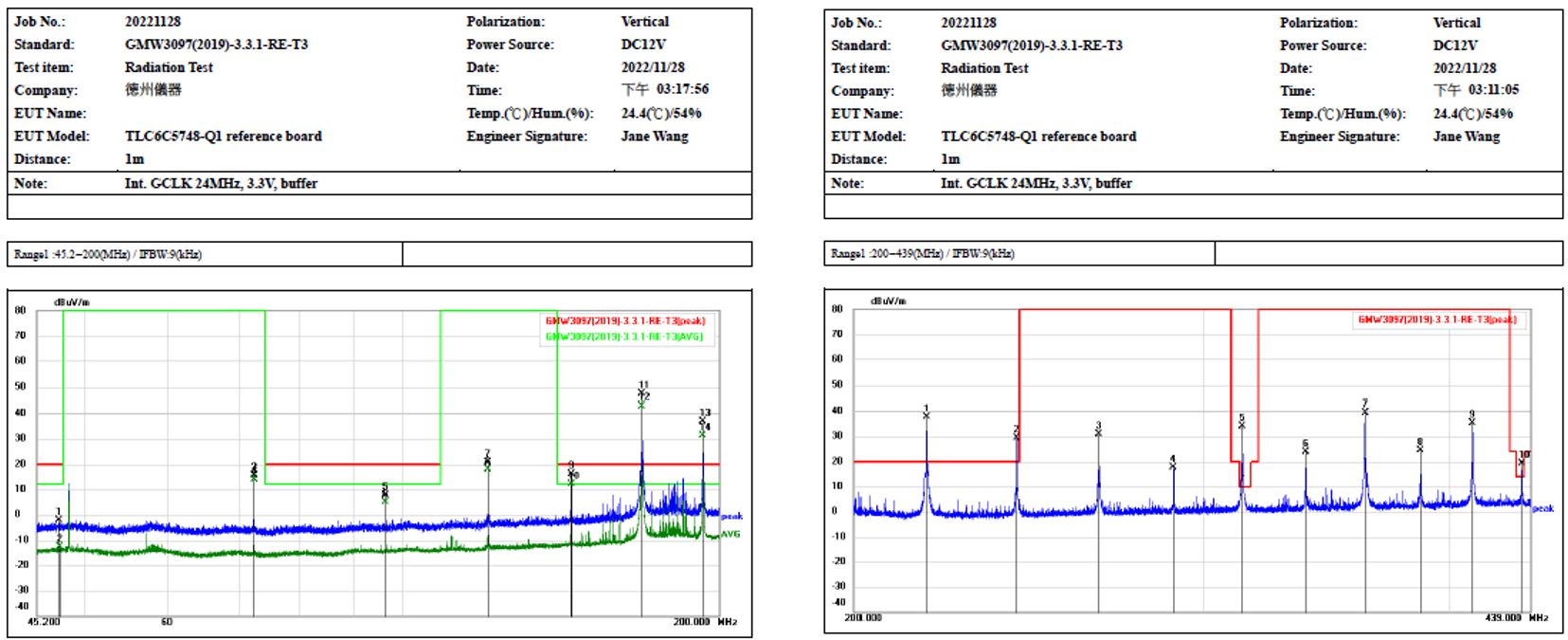

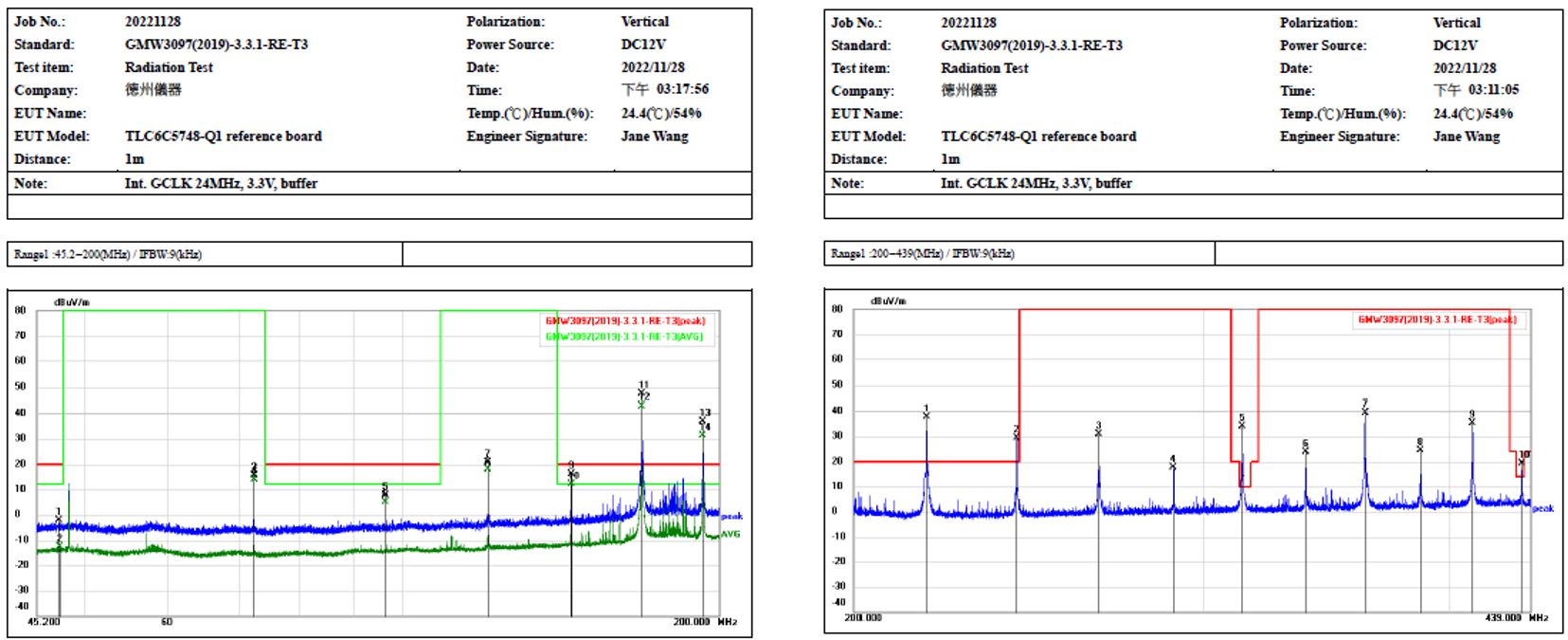

尽管 TLC6C5748-Q1 与接口(LAT、SIN、SCLK、GSCLK)上的 3.3V 或 5V I/O 电压兼容,但 3.3V I/O 电压会导致整个频率范围内的能量较低。图 2-4 展示了 3.3V I/O 测试结果。

图 2-4 使用 3.3V IO 电压设置(垂直方向)从 45MHz 到

439MHz 的测试结果

图 2-4 使用 3.3V IO 电压设置(垂直方向)从 45MHz 到

439MHz 的测试结果ZHCAC48 February 2023 TLC6C5748-Q1

尽管 TLC6C5748-Q1 与接口(LAT、SIN、SCLK、GSCLK)上的 3.3V 或 5V I/O 电压兼容,但 3.3V I/O 电压会导致整个频率范围内的能量较低。图 2-4 展示了 3.3V I/O 测试结果。

图 2-4 使用 3.3V IO 电压设置(垂直方向)从 45MHz 到

439MHz 的测试结果

图 2-4 使用 3.3V IO 电压设置(垂直方向)从 45MHz 到

439MHz 的测试结果