ZHCAC48 February 2023 TLC6C5748-Q1

2.2.2.4 不在 GSCLK 上使用缓冲器

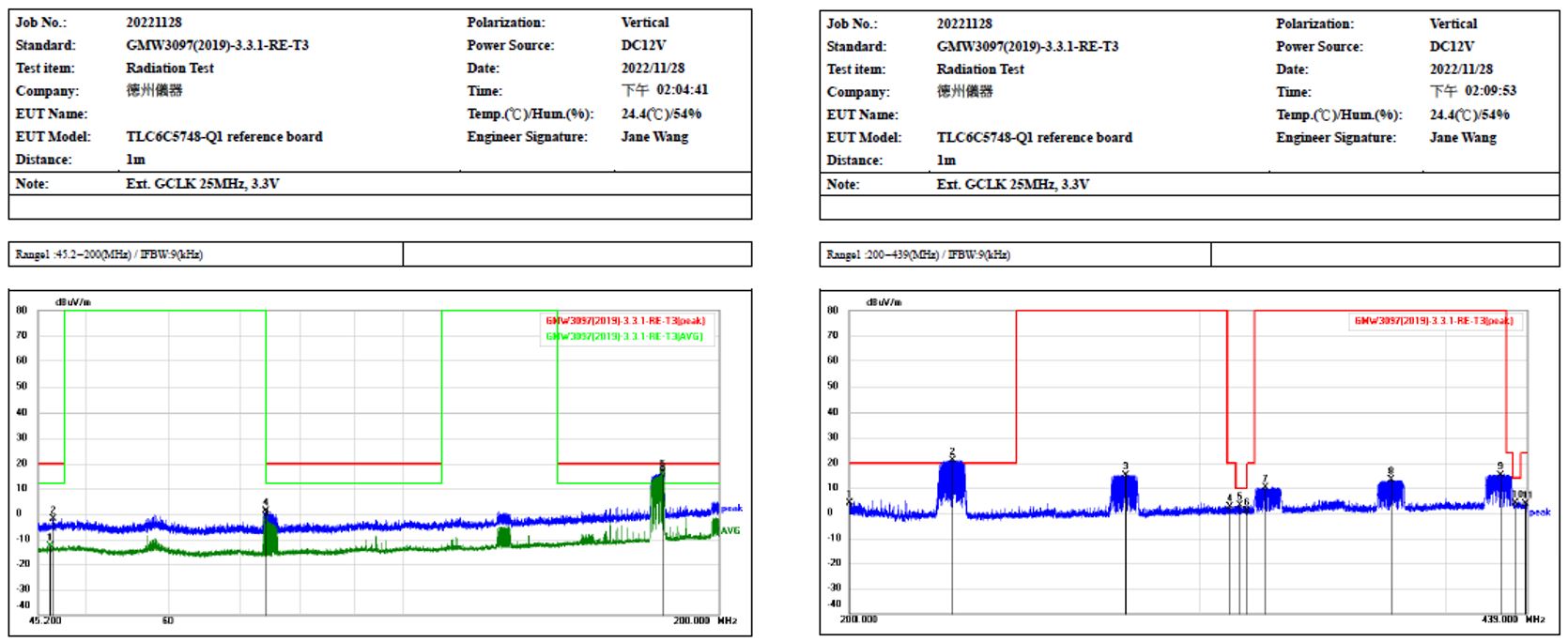

虽然使用具有展频功能的 OSC 作为 GSCLK 可以大大降低 EMI 噪声,但在某些频段仍然超出规格。可以通过降低 GSCLK 能量来降低 EMI。降低 EMI 能量的常用方法是在系统正常运行、信号波形符合规范并留有足够余量的前提下不使用缓冲器。图 2-6 展示了不为 GSCLK 使用缓冲器时的测试结果。

图 2-6 使用 3.3V IO 电压设置、带 SSC 的 GSCLK

并在 45MHz 到 439MHz 范围内移除缓冲器(垂直方向)的测试结果

图 2-6 使用 3.3V IO 电压设置、带 SSC 的 GSCLK

并在 45MHz 到 439MHz 范围内移除缓冲器(垂直方向)的测试结果