ZHCAC48 February 2023 TLC6C5748-Q1

2.2.2.10 基准测试结果

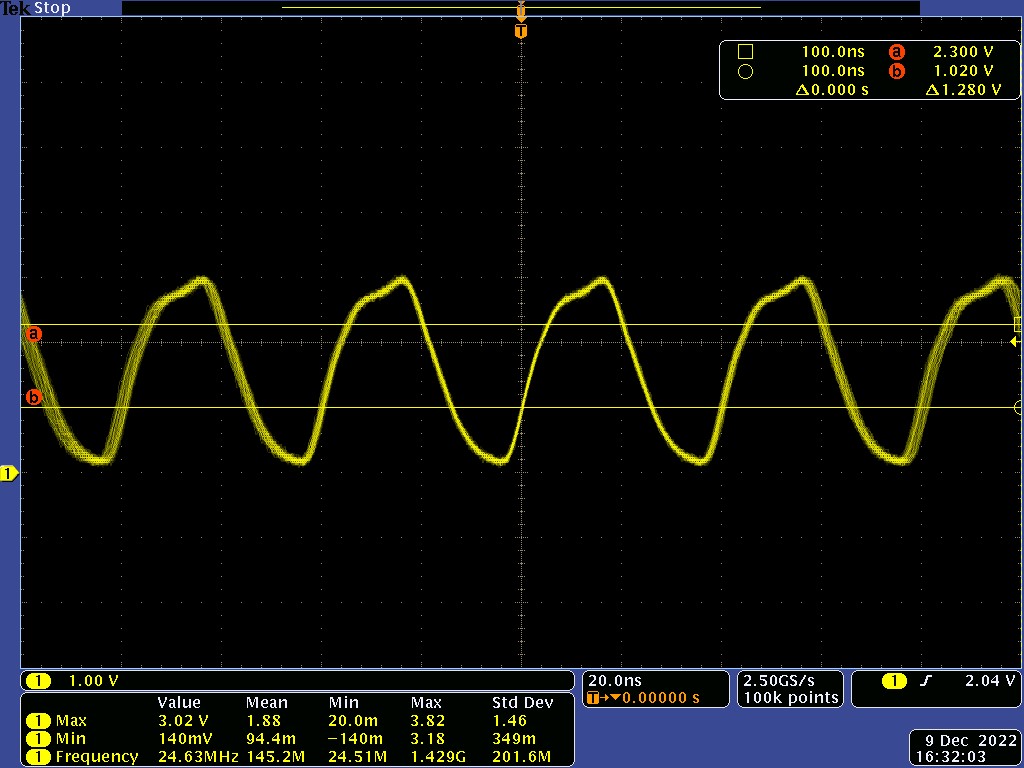

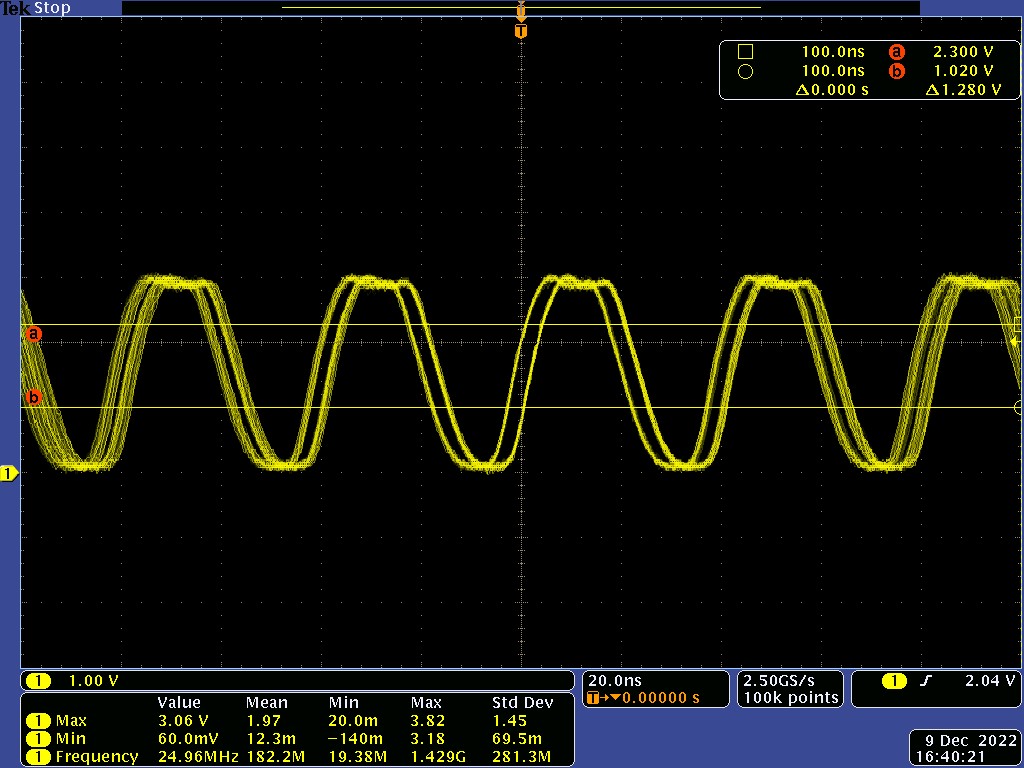

添加对策后,检查信号完整性是否必不可少,尤其是 GSCLK。有时,添加缓冲器时 GSCLK 波形会受到影响。根据数据表,应检查 GSCLK 是否满足芯片标准高/低脉冲大于 10us。对于 TLC6C5748-Q1 结构,检查第一个 TLC6C5748-Q1 和最后一个 TLC6C5748-Q1 GSCLK 引脚,确认是否符合数据表。

图 2-13 第一个 TLC6C5748-Q1 GSCLK

波形

图 2-13 第一个 TLC6C5748-Q1 GSCLK

波形 图 2-14 最后一个 TLC6C5748-Q1 GSCLK

波形

图 2-14 最后一个 TLC6C5748-Q1 GSCLK

波形