ZHCACD6A February 2023 – December 2023 AM62A3 , AM62A3-Q1 , AM62A7 , AM62A7-Q1 , AM62P , AM62P-Q1

3.6.2 布线

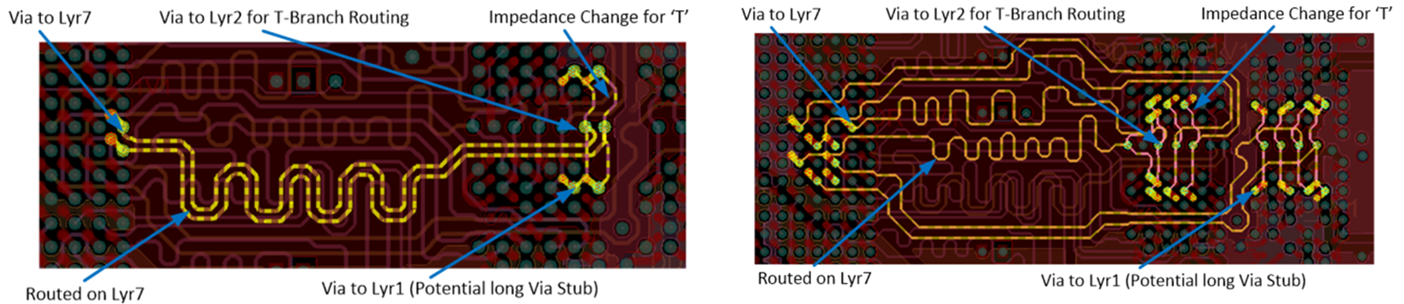

以下 J7 设计示例显示了 10 层 PCB 设计示例上的 LPDDR4 时钟和 CA 布线。时钟以 70Ω 的目标阻抗进行差分布线。为了使 T 分支与布线阻抗相匹配,阻抗需要加倍。这会带来挑战,因为在某些 PCB 堆叠中可能难以实现较高的阻抗。CA 信号的布线目标为 35Ω,T 分支的目标为源阻抗的两倍。

图 3-7 LPDDR4 时钟和 CA 布线示例

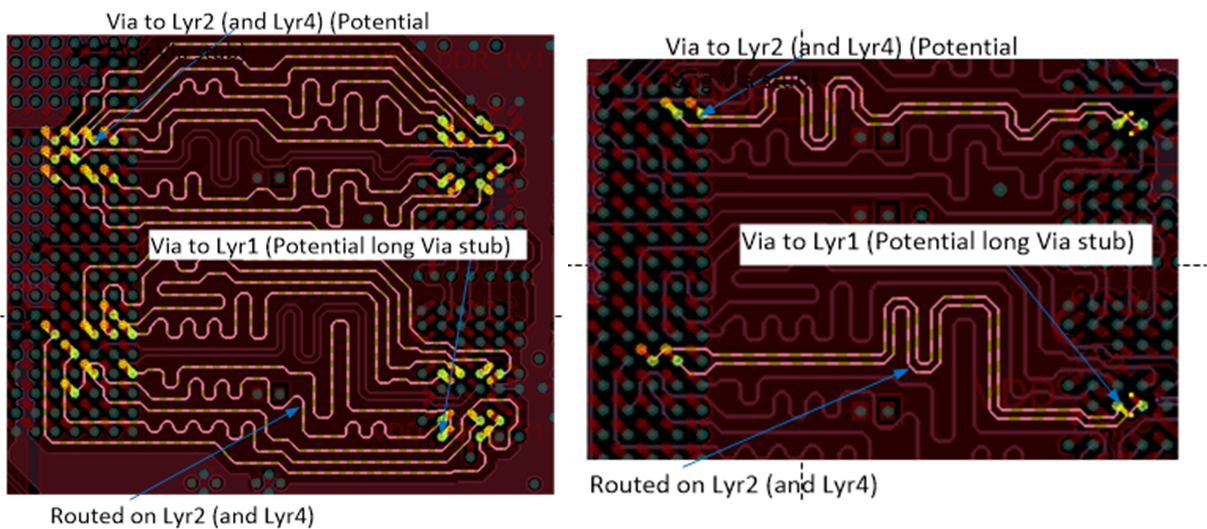

图 3-7 LPDDR4 时钟和 CA 布线示例 在同一个 10 层参考设计中,数据组在第 2 层和第 4 层上布线。由于具有最小过孔行程,使用了上部的层,从而更大限度降低了过孔电感和过孔之间的耦合。数据信号是点对点的,因此不需要 T 分支布线。

图 3-8 LPDDR4 数据字节和 DQS 布线示例

图 3-8 LPDDR4 数据字节和 DQS 布线示例 表 3-8 LPDDR4 性能对布线层的影响(在焊盘上读取)

| 布线层 | 过孔类型 | 背钻 | EW 裕量 (ps) | EH 裕量 (mV) |

|---|---|---|---|---|

| L1、L12 | PTH | 否 | -7.10 | 56.72 |

| L1、L12 | PTH | 是 | -4.86 | 55.71 |

| L1、L3 | PTH | 否 | 5.70 | 40.29 |

| L1、L3 | PTH | 是 | 8.37 | 34.54 |

表 3-9 LPDDR4 性能对布线层的影响(在焊盘上写入)

| 布线层 | 过孔类型 | 背钻 | EW 裕量 (ps) | EH 裕量 (mV) |

|---|---|---|---|---|

| L1、L12 | PTH | 否 | 17.42 | 39.22 |

| L1、L12 | PTH | 是 | 20.04 | 41.93 |

| L1、L3 | PTH | 否 | 27.66 | 41.37 |

| L1、L3 | PTH | 是 | 27.76 | 48.63 |