ZHCACD6A February 2023 – December 2023 AM62A3 , AM62A3-Q1 , AM62A7 , AM62A7-Q1 , AM62P , AM62P-Q1

3.5.1 仿真设置

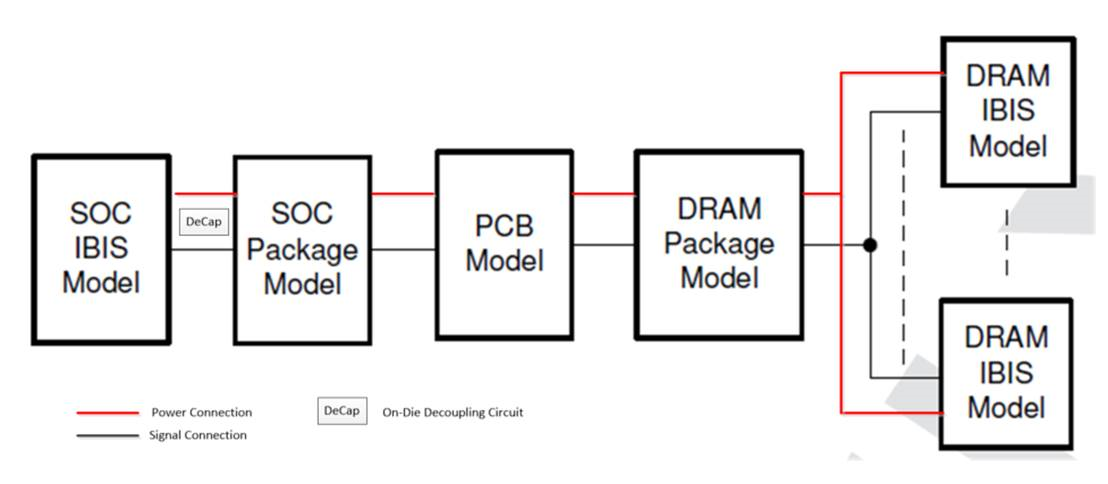

通过连接 SOC IBIS 模型、电路板模型、电源、DRAM 封装模型和 DRAM IBIS 模型,在仿真器中建立系统级原理图。图 3-2所示为典型的系统级 DDR 原理图。

注: 在建立系统原理图时,请注意 DRAM 配置(封装中的芯片数量、列数和通道数)。请注意,DRAM 配置可能还包括片上去耦电路。

图 3-2 典型的系统级 DDR 原理图

图 3-2 典型的系统级 DDR 原理图- LPDDR4 仿真需要针对控制器和存储器的功率感知 IBIS 模型以及支持 DDR 接口通道仿真的仿真器。

- 基于 SPICE 的晶体管级仿真不能用于生成 BER 信号眼图。使用可以处理功率感知 IBIS 仿真并能够为 DDR 接口运行通道仿真的仿真器。

- 与基于 SPICE 的晶体管级仿真相比,IBIS 模型减少了仿真时间,同时精度损失极小。从 5.0 版开始的 IBIS 模型是功率感知模型,可实现同步开关输出 (SSO) 噪声仿真。TI IBIS 模型是一种功率感知 IBIS 模型。

- 使用 SPICE 模型对控制器和 DRAM的 DDR 电源网上的片上去耦电容进行准确建模。这可以确保在 DDR 仿真中实现准确的电源噪声和电源引起的抖动 (PSIJ) 估算。可以从 DRAM 供应商处获得 DRAM 的片上去耦电容信息。

- 使用 SPICE 或 S 参数文件对 DRAM 封装进行建模。这可以从 DRAM 供应商处索取。不建议使用 EBD 模型。

- 请注意,SoC IBIS 模型中有一个包含 RLC 矩阵的封装部分,用于所有信号和电源网(包括 DDR)。可以使用 ibis 模型中的此封装模型,或图 3-2 中所示的 SOC 封装 s 参数模型。不要在仿真中同时使用这两种模型。

- DDR 电源网上的片上去耦电容的 AM62Ax/AM62Px 模型:

****************************************** * On-die Decoupling circuit for AM62Ax/AM62Px (DIE_VDDS_DDR to VSS) ****************************************** * Notes: * Includes on-die decoupling for all DDR signals * * This subcircuit should be added across the AM62Ax/AM62Px IBIS model's * DIE_VDDS_DDR and VSS pins * ****************************************** * x_decouple DIE_VDDS_DDR vss_die AM62A_P_ondie_decoupling_alldq ****************************************** .SUBCKTAM62A_P_ondie_decoupling_alldq DIE_VDDS_DDR vss_die Cvddq_c DIE_VDDS_DDR DIE_VDDS_DDR_c 2.6e-9 Rvddq_c vss_die DIE_VDDS_DDR_c 42.04e-3 .ENDS