ZHCACE4A March 2023 – August 2024 TMS320F2800132 , TMS320F2800133 , TMS320F2800135 , TMS320F2800137 , TMS320F2800152-Q1 , TMS320F2800153-Q1 , TMS320F2800154-Q1 , TMS320F2800155 , TMS320F2800155-Q1 , TMS320F2800156-Q1 , TMS320F2800157 , TMS320F2800157-Q1 , TMS320F280021 , TMS320F280021-Q1 , TMS320F280023 , TMS320F280023-Q1 , TMS320F280023C , TMS320F280025 , TMS320F280025-Q1 , TMS320F280025C , TMS320F280025C-Q1 , TMS320F280033 , TMS320F280034 , TMS320F280034-Q1 , TMS320F280036-Q1 , TMS320F280036C-Q1 , TMS320F280037 , TMS320F280037-Q1 , TMS320F280037C , TMS320F280037C-Q1 , TMS320F280038-Q1 , TMS320F280038C-Q1 , TMS320F280039 , TMS320F280039-Q1 , TMS320F280039C , TMS320F280039C-Q1 , TMS320F28P650DK

4 硬件过采样

为了测试 ADC 过采样,使用了 TMDSCNCD28P65X controlCARD 将输入正弦波转换为数字值。请参阅 TMDSCNCD28P65X controlCARD 信息指南 来为 controlCARD 配置基准电压 VREF 和 JTAG。为了使设置简单,同时减少可能的误差源,使用了内部 1.65V 基准。如果使用外部 VREF,则必须采取额外的步骤。有关 VREF 的更多信息,请参阅 TMS320F28P650DK 实时微控制器技术参考手册 ADC 一章中的电压基准 一节。

如果配置得当,用于 ADC 采样的硬件可以降低环境和信号噪声。在评估过采样性能时,设备可能是噪声源。使用具有高分辨率的信号源,并遵循降低系统噪声的做法进行验证设置。对于本应用手册,使用 Agilent AG33522A 任意波形发生器 (AWG) 作为信号源。通常,分辨率高于 ADC 的信号源会产生更优结果。为了减少获得的 ENOB 值可能出现的偏差,请遵循模拟电路的优秀布局实践。ADC 输入调节也在提高 ADC 的精度方面发挥着作用。有关输入调节的详细信息,请参阅 C2000™ MCU 的 ADC 输入评估。有关 PCB 布局设计建议,请参阅 F2800x C2000™ 实时 MCU 系列的硬件设计指南 应用手册。

在用于硬件过采样的示例中,包含配置 ADC、ePWM 和其他外设的主代码。

对于硬件过采样,SOC 配置有触发中继器,可根据需要生成许多重复脉冲。在此示例中,使用 ePWM 脉冲触发 SOC,结果会累积到累加器中,在过采样时不会丢失值。设置过采样中断,以便在达到中继器计数时触发。中断会运行相应的 ISR,该 ISR 会存储 ADC 结果,如果启用了过采样,则累加结果。

使用触发器中继器的过采样示例 展示了使用触发器中继器进行过采样的示例代码。

使用触发器中继器的过采样示例

// adcA1ISR - ADC A Interrupt 1 ISR

//

__interrupt void adcA1ISR(void)

{

//

// Store the results for A0

//

// myADC0Result = ADC_readResult(ADCARESULT_BASE, ADC_SOC_NUMBER0);

//

// Store the 4 oversampled A0 results together

//

lv_results[nloops++] = (uint16_t)ADC_readPPBSum(ADCARESULT_BASE, ADC_PPB_NUMBER1);

// Clear the interrupt flag

//

ADC_clearInterruptStatus(myADC0_BASE, ADC_INT_NUMBER1);

//

// Check if overflow has occurred

//

if(true == ADC_getInterruptOverflowStatus(myADC0_BASE, ADC_INT_NUMBER1))

{

ADC_clearInterruptOverflowStatus(myADC0_BASE, ADC_INT_NUMBER1);

ADC_clearInterruptStatus(myADC0_BASE, ADC_INT_NUMBER1);

}

//

// Acknowledge the interrupt

//

Interrupt_clearACKGroup(INT_myADC0_1_INTERRUPT_ACK_GROUP);

if(nloops >= numBins)

{

//

// Disable ADC interrupt

//

ADC_disableInterrupt(myADC0_BASE, ADC_INT_NUMBER1);

ESTOP0;

}

}存储了预期数量的结果之后,即可禁用相应的中断,否则 ADC 可以继续转换模拟信号。图 4-1 展示了使用 ePWM 触发中继器进行过采样的基本流程。

图 4-1 硬件过采样的 SOC 流程图

图 4-1 硬件过采样的 SOC 流程图一种很好的设计做法是增加 ePWM 时基以允许更长的转换时间,从而为控制循环提供更多完成时间。这降低了可正确测量的最大频率,因为 ADC 不会经常触发。

输入频率会影响可使用的过采样因子。对于频率更高或需要以更高速率进行采样的信号,由于所需的软件开销,需要使用更低的过采样因子。为了确定不大可能丢失数据的最大输入频率,需要控制循环和过采样所需的周期数。周期计数包括任何用户相关操作(例如 ISR 处理)或每次获取新样本时需要执行的处理。图 4-2 展示了在对信号进行采样时这些时序发挥作用的地方。在此图中,过采样和控制循环时间包括用于中断延迟和 ISR 执行的系统时钟周期。请注意,控制循环结束到下一个 ADC 触发器到达之间存在一些缓冲时间,因此处理不会阻止触发发生,数据也不会丢失。图 4-3 显示,当转换、过采样和控制循环的总时间超过 ePWM 周期时,丢失了数据。解决此问题的方法是延长周期,在本示例中,需要延长 ePWM 时基才能进一步移动触发器。

图 4-2 硬件过采样中信号采样的时序

图 4-2 硬件过采样中信号采样的时序 图 4-3 硬件过采样中信号采样的错误时序

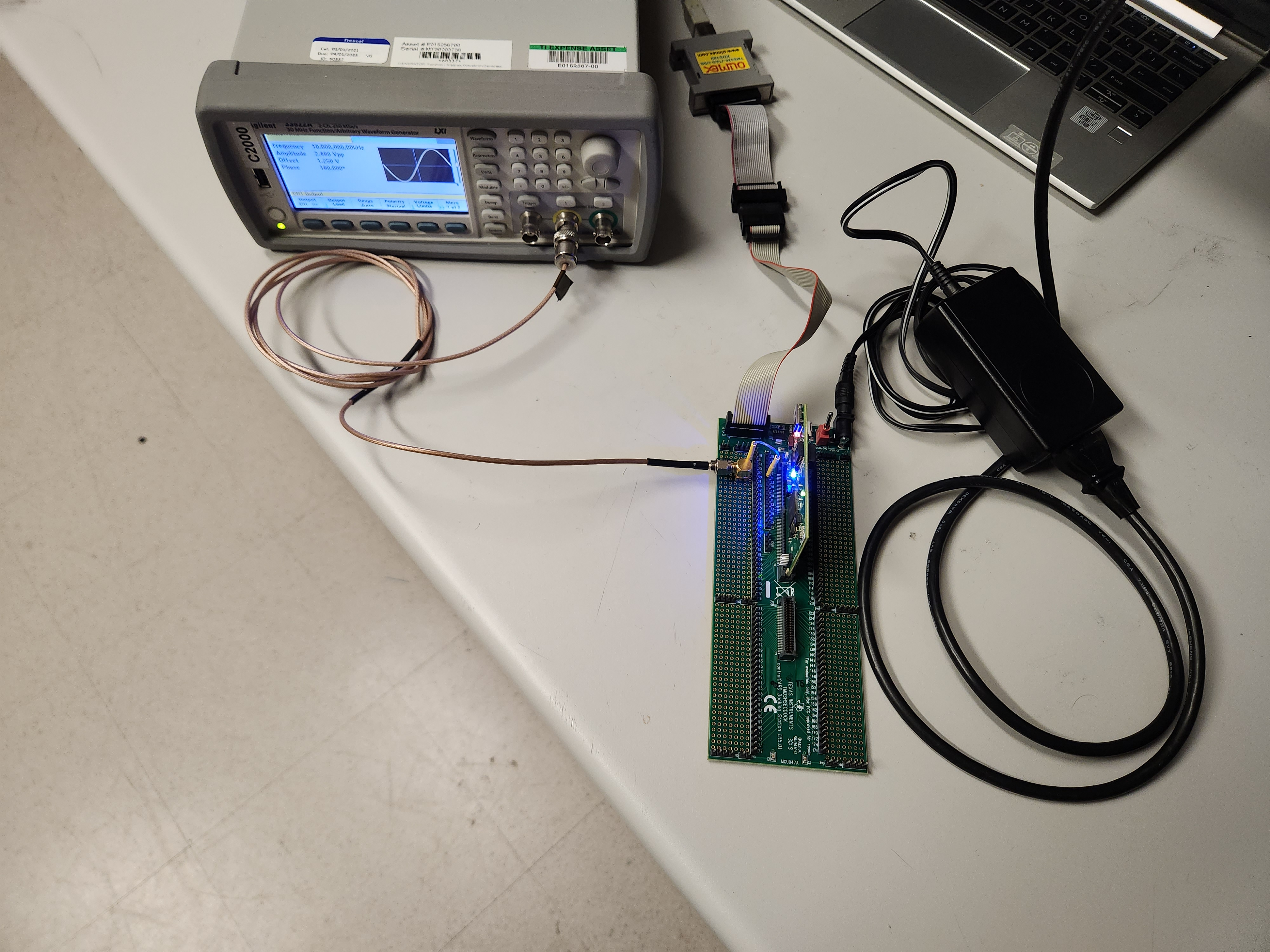

图 4-3 硬件过采样中信号采样的错误时序 图 4-4 总体硬件设置

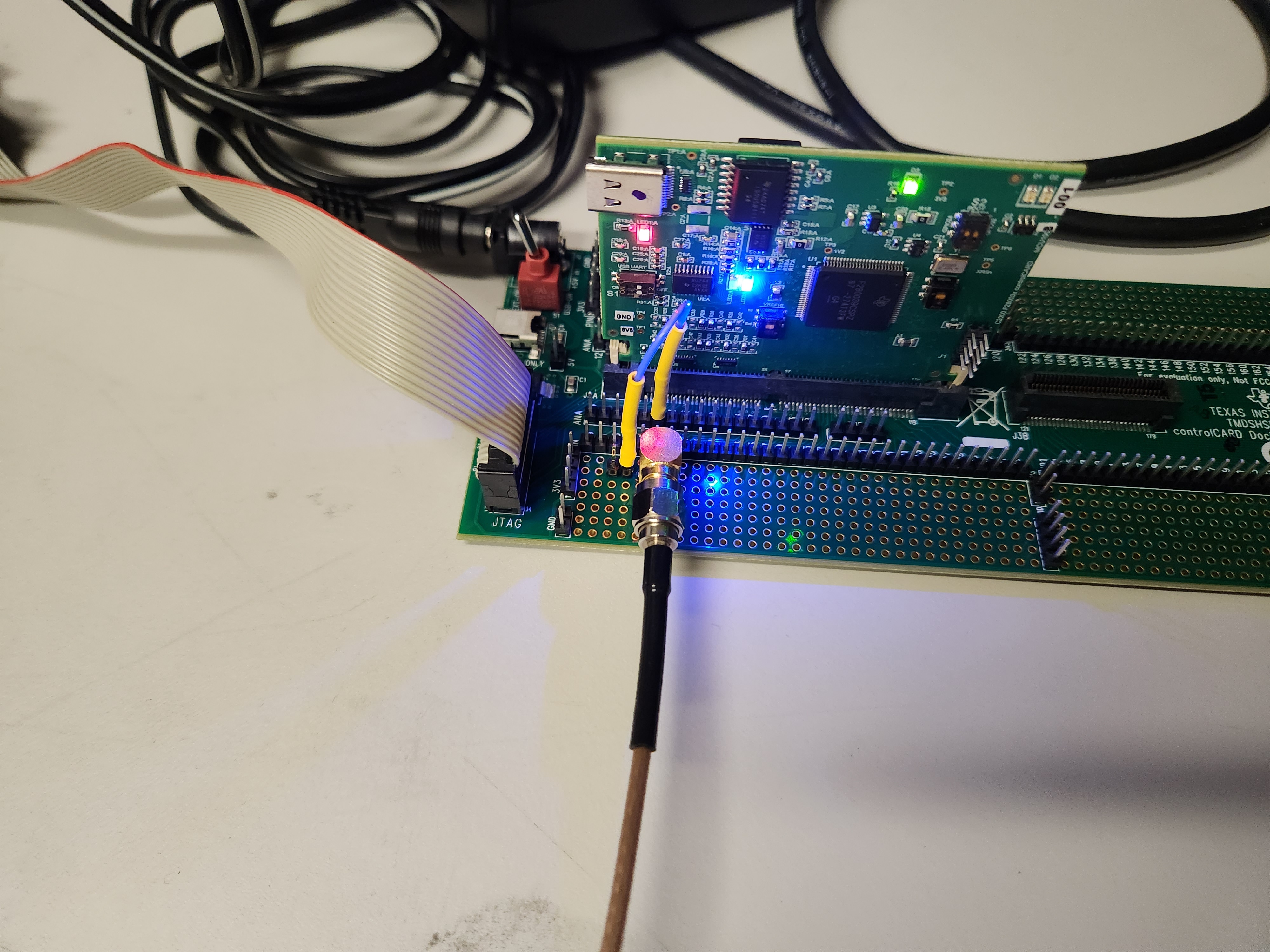

图 4-4 总体硬件设置 图 4-5 接线设置

图 4-5 接线设置