ZHCACF2 March 2023 AM2631 , AM2632 , AM2634

3.2 处理高阻抗传感器

某些应用要求 ADC 在相对高阻抗的传感器上采样 5V 信号。该传感器在某些情况下可能无法驱动或支持 R1+R2 的直接负载,尤其是当它们不是很高时。为了解决这个问题,我们可以增加 R1+R2 直至满足所需的负载限制,并使用非常大的 Cs 来帮助 ADC 采样。

例如,我们可以使用 R1=1.7M 和 R2=3.3M 以及 Cs=30nF 来提供一个网络,该网络为传感器提供 5M 阻抗,同时即使在最高采样率下也能实现纯净的 ADC 采样。

使用较高的 R1 和 R2 值时,必须注意 ADC 输入负载对电路精度的影响。例如,在此用例中,如果 ADC 配置为切换到该传感器并每 1us 对电阻梯进行一次采样,这将提供最坏情况下的平均负载 R=1us/(Cp+Ch) ≈100K,这个值与电阻梯相比非常大,因此会在测量中导致相当大的误差。为了减小这一误差,我们只需降低采样率。如果我们每 1ms 检测一次该输入,此阻抗将跳至大约 100M,但不会对精度产生任何影响。这种更新速率降低问题通常不是高阻抗传感器的问题,这些传感器本身就很慢。此外,该阶梯网络还将有一个大约 4Hz 的模拟滤波器,所以每 1us 的采样与每 1ms 的采样没有什么不同。还有一个额外的好处,此滤波有助于在许多用例中消除系统噪声。

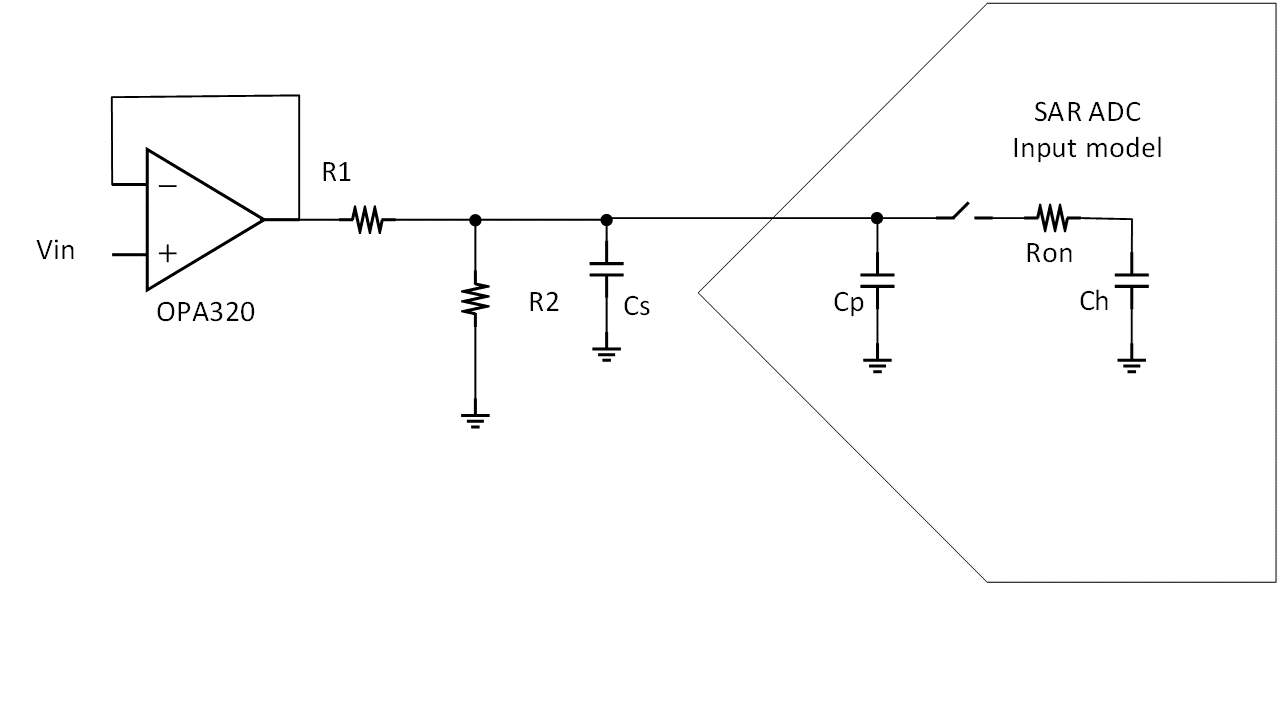

解决该问题的一种更好但成本稍高的方法是使用具有高输入阻抗和低输出阻抗的运算放大器。TI 的高性能低成本运算放大器具有非常广泛的选择范围和许多应用手册。下面展示了一个采用常见 OPA320 或 OPA320-Q1 器件的示例。一个具有低输出阻抗的高阻抗单位增益运算放大器将驱动电阻分压器,并提供与电阻分压器和采样电容器的隔离。

图 3-3 运算放大器驱动电路