ZHCACF6A february 2021 – march 2023 TMS320F2800132 , TMS320F2800133 , TMS320F2800135 , TMS320F2800137 , TMS320F2800152-Q1 , TMS320F2800153-Q1 , TMS320F2800154-Q1 , TMS320F2800155 , TMS320F2800155-Q1 , TMS320F2800156-Q1 , TMS320F2800157 , TMS320F2800157-Q1 , TMS320F280021 , TMS320F280021-Q1 , TMS320F280023 , TMS320F280023-Q1 , TMS320F280023C , TMS320F280025 , TMS320F280025-Q1 , TMS320F280025C , TMS320F280025C-Q1 , TMS320F280033 , TMS320F280034 , TMS320F280034-Q1 , TMS320F280036-Q1 , TMS320F280036C-Q1 , TMS320F280037 , TMS320F280037-Q1 , TMS320F280037C , TMS320F280037C-Q1 , TMS320F280038-Q1 , TMS320F280038C-Q1 , TMS320F280039 , TMS320F280039-Q1 , TMS320F280039C , TMS320F280039C-Q1 , TMS320F280040-Q1 , TMS320F280040C-Q1 , TMS320F280041 , TMS320F280041-Q1 , TMS320F280041C , TMS320F280041C-Q1 , TMS320F280045 , TMS320F280048-Q1 , TMS320F280048C-Q1 , TMS320F280049 , TMS320F280049-Q1 , TMS320F280049C , TMS320F280049C-Q1 , TMS320F28075 , TMS320F28075-Q1 , TMS320F28076 , TMS320F28374D , TMS320F28374S , TMS320F28375D , TMS320F28375S , TMS320F28375S-Q1 , TMS320F28376D , TMS320F28376S , TMS320F28377D , TMS320F28377D-EP , TMS320F28377D-Q1 , TMS320F28377S , TMS320F28377S-Q1 , TMS320F28378D , TMS320F28378S , TMS320F28379D , TMS320F28379D-Q1 , TMS320F28379S , TMS320F28384D , TMS320F28384D-Q1 , TMS320F28384S , TMS320F28384S-Q1 , TMS320F28386D , TMS320F28386D-Q1 , TMS320F28386S , TMS320F28386S-Q1 , TMS320F28388D , TMS320F28388S , TMS320F28P650DH , TMS320F28P650DK , TMS320F28P650SH , TMS320F28P650SK , TMS320F28P659DH-Q1 , TMS320F28P659DK-Q1 , TMS320F28P659SH-Q1

4.2 配置仿真参数

电荷共享仿真需要完成的主要配置是设置采样率。这是由分段线性电压源 tacq 和 tdis 的设置控制的。

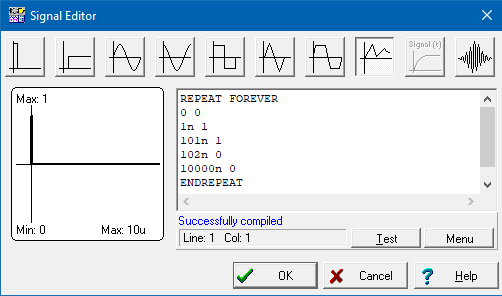

图 4-3 显示了在 100ns 采集窗口和 100kHz 采样率下的示例 tacq 时序配置。前四行将 S+H 窗口配置为在 0 到 102ns 之间发生,上升和下降时间为 1ns。最后一行(主要关注点)配置波形重复的频率。这有效地设置了采样率,10000ns (10µs) 相当于 100kHz 采样。

图 4-3 tacq 的示例时序(分段线性)

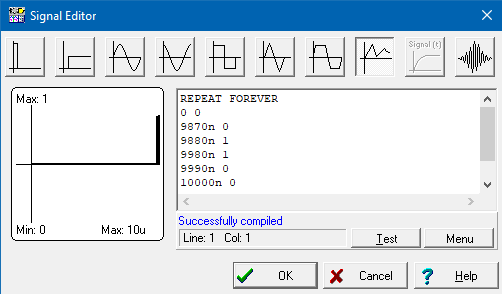

图 4-3 tacq 的示例时序(分段线性)图 4-4 显示了 100ns 放电周期和 100kHz 采样率的示例 tdis 时序配置。前五行指定 100ns 的放电周期,从 9.87µs 开始有 10ns 的上升和下降时间。最后一行配置波形重复的频率。这有效地设置了采样率,10000ns (10µs) 相当于 100kHz 采样。确保 tdis 和 tacq 时序的最后一行始终完全匹配!该放电周期不必恰好在触发周期结束时发生,因此仅通过更改最后一行来更改采样率是可以接受的。例如,如果将 tdis 和 tacq 的最后一行更改为 20000ns,则会将采样率更改为 50kHz。不过,请确保放电周期不与 tacq 中的 S+H 周期重叠,否则将导致输入短接至接地端,而不是为 CH 充电。

图 4-4 tdis 的示例时序(分段线性)

图 4-4 tdis 的示例时序(分段线性)请注意,这些时序配置为模拟以 100kHz 频率触发的转换。特定通道上这种较慢的采样率是电荷共享输入设计的典型值(而不是最大 ADC 采样率下的背靠背连续转换)。通过修改 tacq 和 tdis 时序源的周期,可以修改触发频率以匹配实际应用的 ePWM 触发频率。不过,请务必确保触发周期大于 ADC 转换的总 S+H 加采集时间。器件特定数据手册的“ADC 时序”表中提供了 ADC 转换时间。