ZHCACF7A june 2021 – march 2023 TMS320F2800132 , TMS320F2800133 , TMS320F2800135 , TMS320F2800137 , TMS320F2800152-Q1 , TMS320F2800153-Q1 , TMS320F2800154-Q1 , TMS320F2800155 , TMS320F2800155-Q1 , TMS320F2800156-Q1 , TMS320F2800157 , TMS320F2800157-Q1 , TMS320F280021 , TMS320F280021-Q1 , TMS320F280023 , TMS320F280023-Q1 , TMS320F280023C , TMS320F280025 , TMS320F280025-Q1 , TMS320F280025C , TMS320F280025C-Q1 , TMS320F280033 , TMS320F280034 , TMS320F280034-Q1 , TMS320F280036-Q1 , TMS320F280036C-Q1 , TMS320F280037 , TMS320F280037-Q1 , TMS320F280037C , TMS320F280037C-Q1 , TMS320F280038-Q1 , TMS320F280038C-Q1 , TMS320F280039 , TMS320F280039-Q1 , TMS320F280039C , TMS320F280039C-Q1 , TMS320F280040-Q1 , TMS320F280040C-Q1 , TMS320F280041 , TMS320F280041-Q1 , TMS320F280041C , TMS320F280041C-Q1 , TMS320F280045 , TMS320F280048-Q1 , TMS320F280048C-Q1 , TMS320F280049 , TMS320F280049-Q1 , TMS320F280049C , TMS320F280049C-Q1 , TMS320F28075 , TMS320F28075-Q1 , TMS320F28076 , TMS320F28374D , TMS320F28374S , TMS320F28375D , TMS320F28375S , TMS320F28375S-Q1 , TMS320F28376D , TMS320F28376S , TMS320F28377D , TMS320F28377D-EP , TMS320F28377D-Q1 , TMS320F28377S , TMS320F28377S-Q1 , TMS320F28378D , TMS320F28378S , TMS320F28379D , TMS320F28379D-Q1 , TMS320F28379S , TMS320F28384D , TMS320F28384D-Q1 , TMS320F28384S , TMS320F28384S-Q1 , TMS320F28386D , TMS320F28386D-Q1 , TMS320F28386S , TMS320F28386S-Q1 , TMS320F28388D , TMS320F28388S , TMS320F28P650DH , TMS320F28P650DK , TMS320F28P650SH , TMS320F28P650SK , TMS320F28P659DH-Q1 , TMS320F28P659DK-Q1 , TMS320F28P659SH-Q1

4.2 专用 ADC 的趋稳机制

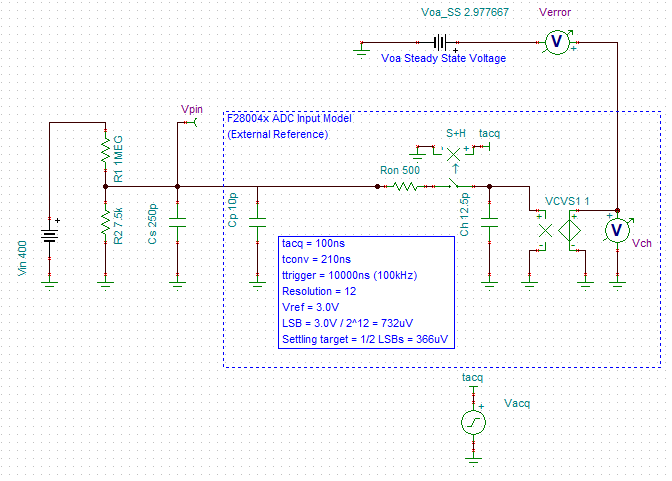

图 4-2 展示了按专用 ADC 概念中所述重新排列示例系统后对前几个稳定周期进行仿真的设置。这里将使用 100ns S+H 窗口,该窗口比先前确定的正常条件 (11.8μs) 下良好趋稳所需的时间短得多。请注意,输入模型中在采样之间对 S+H 电容器放电的部分已被移除,因此 CH 将在采样之间保留其电荷。最后,请注意,仿真配置为 CH 上的初始电压条件为 0V,而分压器输出电压接近满量程 (3.0V)。这将产生一个与满量程输入设置等效的仿真。

图 4-2 专用 ADC 上 V2 的仿真原理图

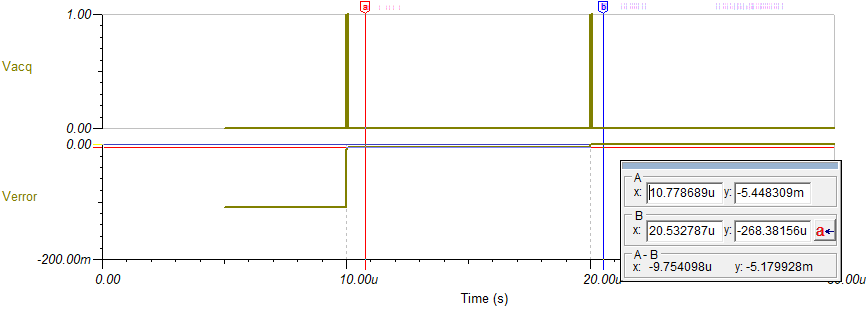

图 4-2 专用 ADC 上 V2 的仿真原理图运行 30µs 的瞬态仿真会得出如 图 4-3 所示的结果。第一次采样后的稳定误差约为 100mV,随后在第二次和第三次采样后分别降至 5.4mV 和 0.27mV。由于 3.0V ADC 范围内的 1/2 LSB 趋稳约为 0.37mV,该系统最终在响应满量程阶跃响应时实现了良好的趋稳!不过,这需要三个采样周期 (30μs),并假定信号在阶跃响应后保持静止。

图 4-3 专用 ADC 上 V2 电路的趋稳仿真

图 4-3 专用 ADC 上 V2 电路的趋稳仿真这些结果非常有趣的是,对于该电路拓扑,预计稳定时间为 11.8μs,但 ADC 仅在三次突发 100ns 时才会打开 S+H 窗口,从而导致总采样时间为 300ns。那么该电路如何实现良好的趋稳呢?

请注意,对于每个样本,误差会按比例缩小大约 20 倍。这对应于外部 ADC 输入电容 CS(本例中为 250pF)与内部 ADC S+H 电容 CH(本例中为 12.5pF)之比。当 S+H 首次打开时,这两个电容器会快速均衡,将 CH 充电至 CS 上输入电压的 95%。