ZHCACF7A june 2021 – march 2023 TMS320F2800132 , TMS320F2800133 , TMS320F2800135 , TMS320F2800137 , TMS320F2800152-Q1 , TMS320F2800153-Q1 , TMS320F2800154-Q1 , TMS320F2800155 , TMS320F2800155-Q1 , TMS320F2800156-Q1 , TMS320F2800157 , TMS320F2800157-Q1 , TMS320F280021 , TMS320F280021-Q1 , TMS320F280023 , TMS320F280023-Q1 , TMS320F280023C , TMS320F280025 , TMS320F280025-Q1 , TMS320F280025C , TMS320F280025C-Q1 , TMS320F280033 , TMS320F280034 , TMS320F280034-Q1 , TMS320F280036-Q1 , TMS320F280036C-Q1 , TMS320F280037 , TMS320F280037-Q1 , TMS320F280037C , TMS320F280037C-Q1 , TMS320F280038-Q1 , TMS320F280038C-Q1 , TMS320F280039 , TMS320F280039-Q1 , TMS320F280039C , TMS320F280039C-Q1 , TMS320F280040-Q1 , TMS320F280040C-Q1 , TMS320F280041 , TMS320F280041-Q1 , TMS320F280041C , TMS320F280041C-Q1 , TMS320F280045 , TMS320F280048-Q1 , TMS320F280048C-Q1 , TMS320F280049 , TMS320F280049-Q1 , TMS320F280049C , TMS320F280049C-Q1 , TMS320F28075 , TMS320F28075-Q1 , TMS320F28076 , TMS320F28374D , TMS320F28374S , TMS320F28375D , TMS320F28375S , TMS320F28375S-Q1 , TMS320F28376D , TMS320F28376S , TMS320F28377D , TMS320F28377D-EP , TMS320F28377D-Q1 , TMS320F28377S , TMS320F28377S-Q1 , TMS320F28378D , TMS320F28378S , TMS320F28379D , TMS320F28379D-Q1 , TMS320F28379S , TMS320F28384D , TMS320F28384D-Q1 , TMS320F28384S , TMS320F28384S-Q1 , TMS320F28386D , TMS320F28386D-Q1 , TMS320F28386S , TMS320F28386S-Q1 , TMS320F28388D , TMS320F28388S , TMS320F28P650DH , TMS320F28P650DK , TMS320F28P650SH , TMS320F28P650SK , TMS320F28P659DH-Q1 , TMS320F28P659DK-Q1 , TMS320F28P659SH-Q1

3.1 示例系统

假设一个具有以下 ADC 参数的系统:

- F280049 C2000 MCU 以 12 位外部基准模式工作

- ADC 由 100kHz ePWM 触发源 (ePWM1 SOCA) 驱动

- 使用了两个 ADC:ADCA 和 ADCB

- 要转换四个电压:V1 到 V4

- V1 和 V2 分配给 ADCA,V3 和 V4 分配给 ADCB

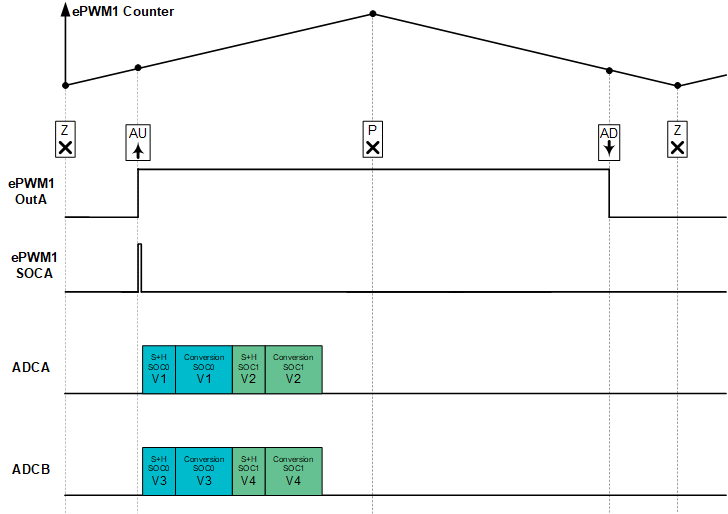

图 3-1 提供了示例系统的时序图。

图 3-1 示例系统时序

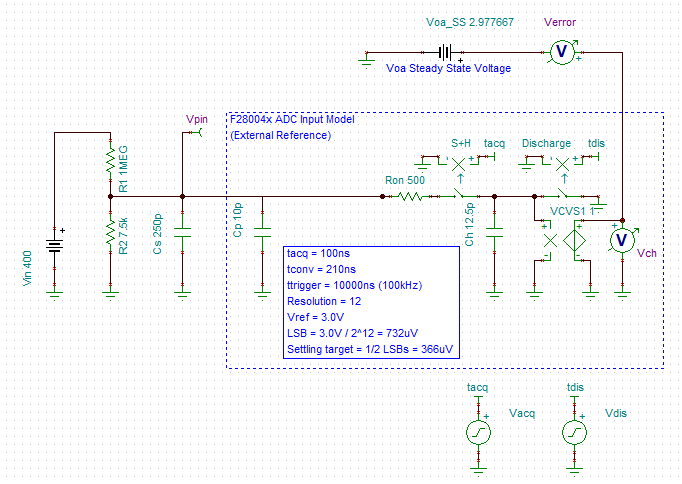

图 3-1 示例系统时序此外,假设 V2 是一个高压检测电路,它使用由 1MΩ 和 7.5kΩ 电阻器组成的分压器来将 400V 信号下调至与 ADC 兼容的 3.0V 范围。分压器直接驱动 ADC 输入(输入端中没有运算放大器进行缓冲),并且外部电容器已选为 250pF。图 3-2 展示了这个电路的原理图。

图 3-2 V2 的示例系统原理图

图 3-2 V2 的示例系统原理图如后续各节所示,很难选择一个足够长的 S+H 持续时间来使该电路实现可接受的稳定性能,并且 100kHz 的采样率也太高,无法支持电荷共享输入设计。因此,需要使用其他方法来缓解本文档后面讨论的存储器串扰。