ZHCACF8 march 2023 TMS320F2800132 , TMS320F2800133 , TMS320F2800135 , TMS320F2800137 , TMS320F2800152-Q1 , TMS320F2800153-Q1 , TMS320F2800154-Q1 , TMS320F2800155 , TMS320F2800155-Q1 , TMS320F2800156-Q1 , TMS320F2800157 , TMS320F2800157-Q1 , TMS320F280021 , TMS320F280021-Q1 , TMS320F280023 , TMS320F280023-Q1 , TMS320F280023C , TMS320F280025 , TMS320F280025-Q1 , TMS320F280025C , TMS320F280025C-Q1 , TMS320F280033 , TMS320F280034 , TMS320F280034-Q1 , TMS320F280036-Q1 , TMS320F280036C-Q1 , TMS320F280037 , TMS320F280037-Q1 , TMS320F280037C , TMS320F280037C-Q1 , TMS320F280038-Q1 , TMS320F280038C-Q1 , TMS320F280039 , TMS320F280039-Q1 , TMS320F280039C , TMS320F280039C-Q1 , TMS320F280040-Q1 , TMS320F280040C-Q1 , TMS320F280041 , TMS320F280041-Q1 , TMS320F280041C , TMS320F280041C-Q1 , TMS320F280045 , TMS320F280048-Q1 , TMS320F280048C-Q1 , TMS320F280049 , TMS320F280049-Q1 , TMS320F280049C , TMS320F280049C-Q1 , TMS320F28075 , TMS320F28075-Q1 , TMS320F28076 , TMS320F28374D , TMS320F28374S , TMS320F28375D , TMS320F28375S , TMS320F28375S-Q1 , TMS320F28376D , TMS320F28376S , TMS320F28377D , TMS320F28377D-EP , TMS320F28377D-Q1 , TMS320F28377S , TMS320F28377S-Q1 , TMS320F28378D , TMS320F28378S , TMS320F28379D , TMS320F28379D-Q1 , TMS320F28379S , TMS320F28384D , TMS320F28384D-Q1 , TMS320F28384S , TMS320F28384S-Q1 , TMS320F28386D , TMS320F28386D-Q1 , TMS320F28386S , TMS320F28386S-Q1 , TMS320F28388D , TMS320F28388S , TMS320F28P650DH , TMS320F28P650DK , TMS320F28P650SH , TMS320F28P650SK , TMS320F28P659DH-Q1 , TMS320F28P659DK-Q1 , TMS320F28P659SH-Q1

3.7 执行初始瞬态分析

现在电路已设置好用于仿真,第一步是运行基本瞬态分析,以确保一切正常运行并检查初始建立。在 PSpice for TI 中执行瞬态分析需要创建时域(瞬态)仿真配置文件。创建仿真配置文件后,请转到“PSpice”➔“Run”以执行分析。

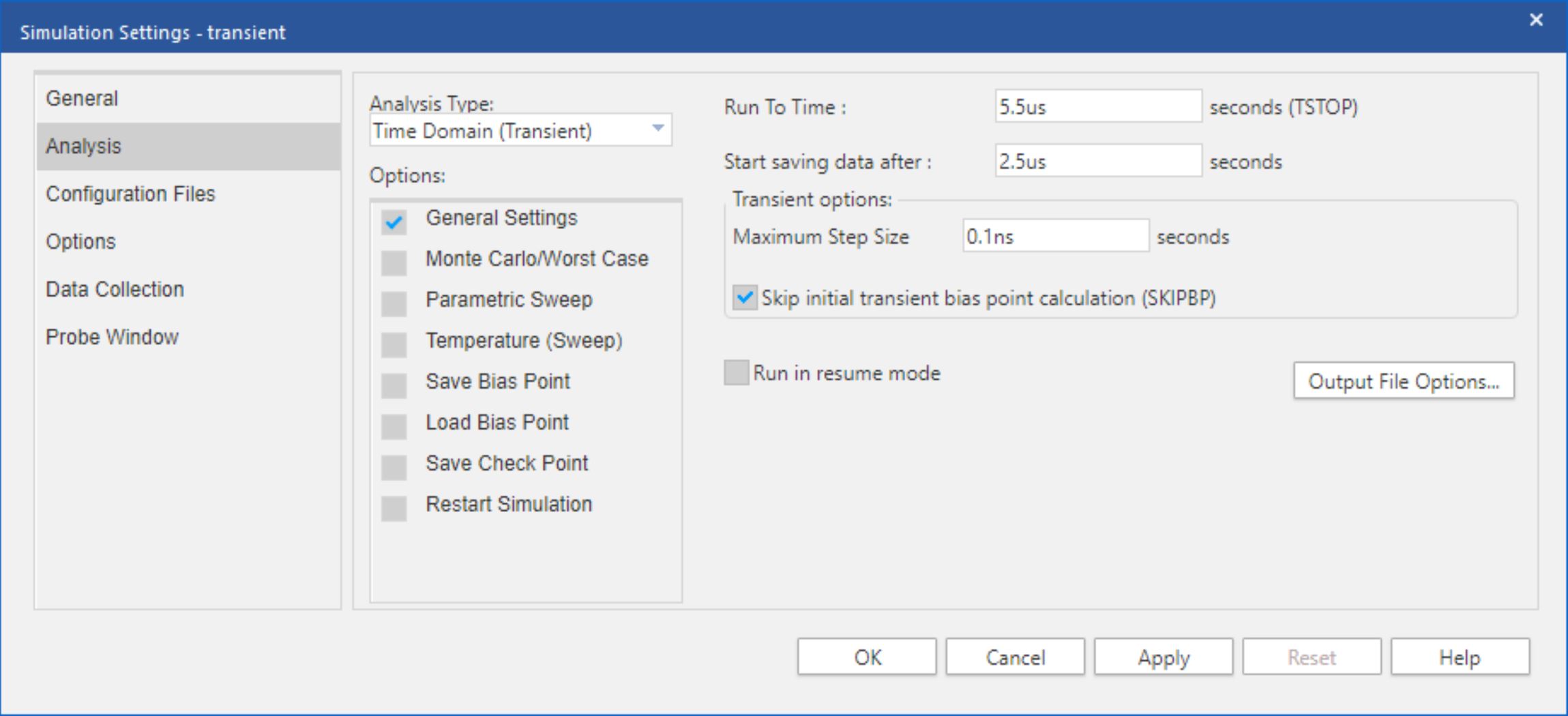

应在让电路稳定几个采样周期后捕获建立,因此选择 2.5μs 至 5.5μs 的时间周期,如图 3-10 所示。这样便可捕获完整的第 3 个和第 4 个采样周期(由于触发频率为 1MHz,因此每个周期为 1μs)。选择 0.1ns 的最大步长,以生成足够精细的仿真结果。

图 3-10 F280049 瞬态分析仿真配置文件示例

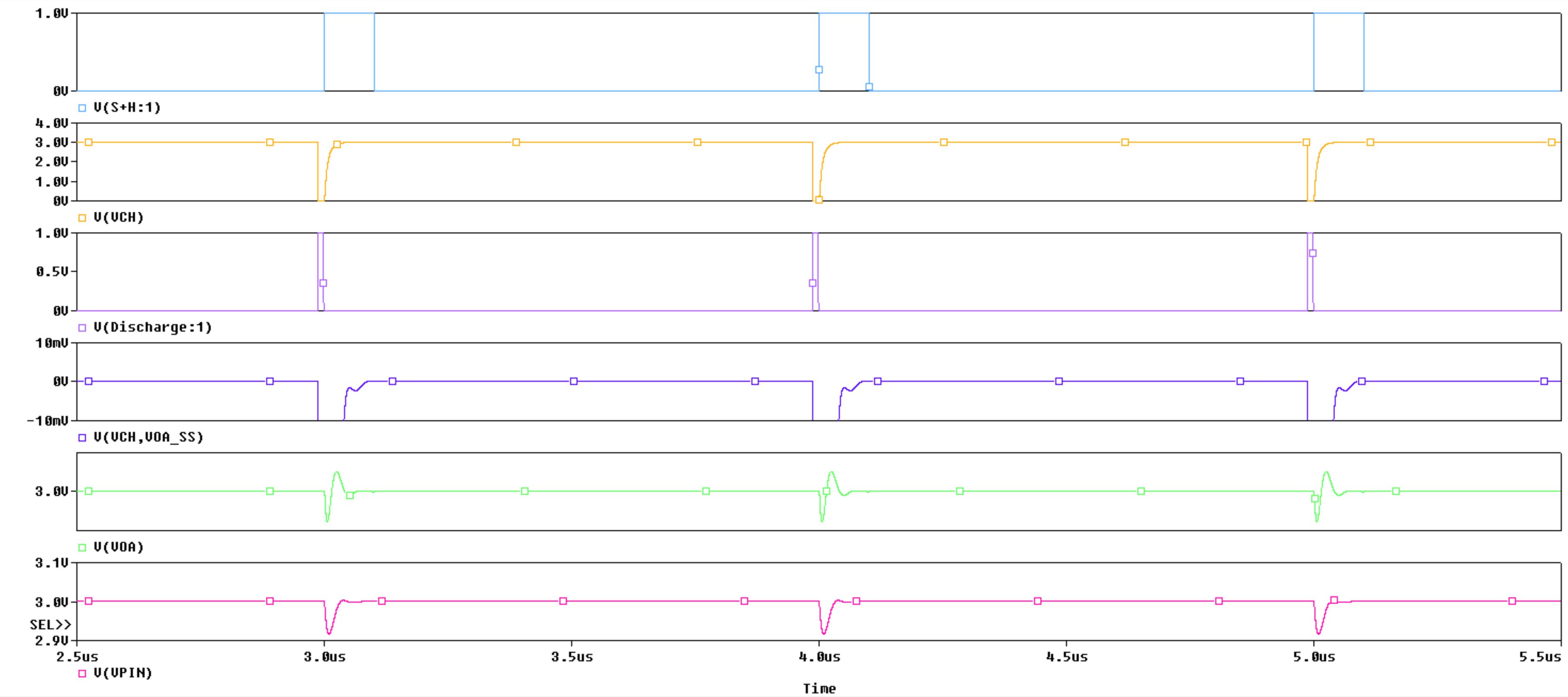

图 3-10 F280049 瞬态分析仿真配置文件示例执行分析后,将输出波形分离到不同的图上。将 Vacq 范围设置为 0V 至 +1V。将 Vch 范围设置为 0V 至 +4V。将 Vdis 范围设置为 0V 至 +1V。将 Verror 范围设置为 -10mV 至 +10mV。将 Voa 范围设置为 +2.9V 至 +3.1V。最后,将 Vpin 范围设置为 +2.9V 至 +3.1V。或者,使用 PSpice for TI 仿真窗口左上角的菜单转到“Window”➔“Display Control...”,以访问 TI 提供的预设显示配置列表。恢复“Transient Results”显示配置。请注意,这些预设显示配置仅在与本应用报告捆绑的 PSpice for TI 工程中可用。图 3-11 显示了瞬态仿真的输出波形。从该输出中可以清楚地看到:

- 放电和采集时间符合预期

- Voa 和 Vpin 上的瞬变幅度合理(小于 100mV,因此信号建立将视为小信号事件)

- Verror 稳定至约 69µV,这完全处于 366µV 的误差目标范围内

图 3-11 F280049 初始瞬态结果示例

图 3-11 F280049 初始瞬态结果示例