ZHCACH2 march 2023 PCA9306

3.6 上升时间是否符合 I2C 标准?

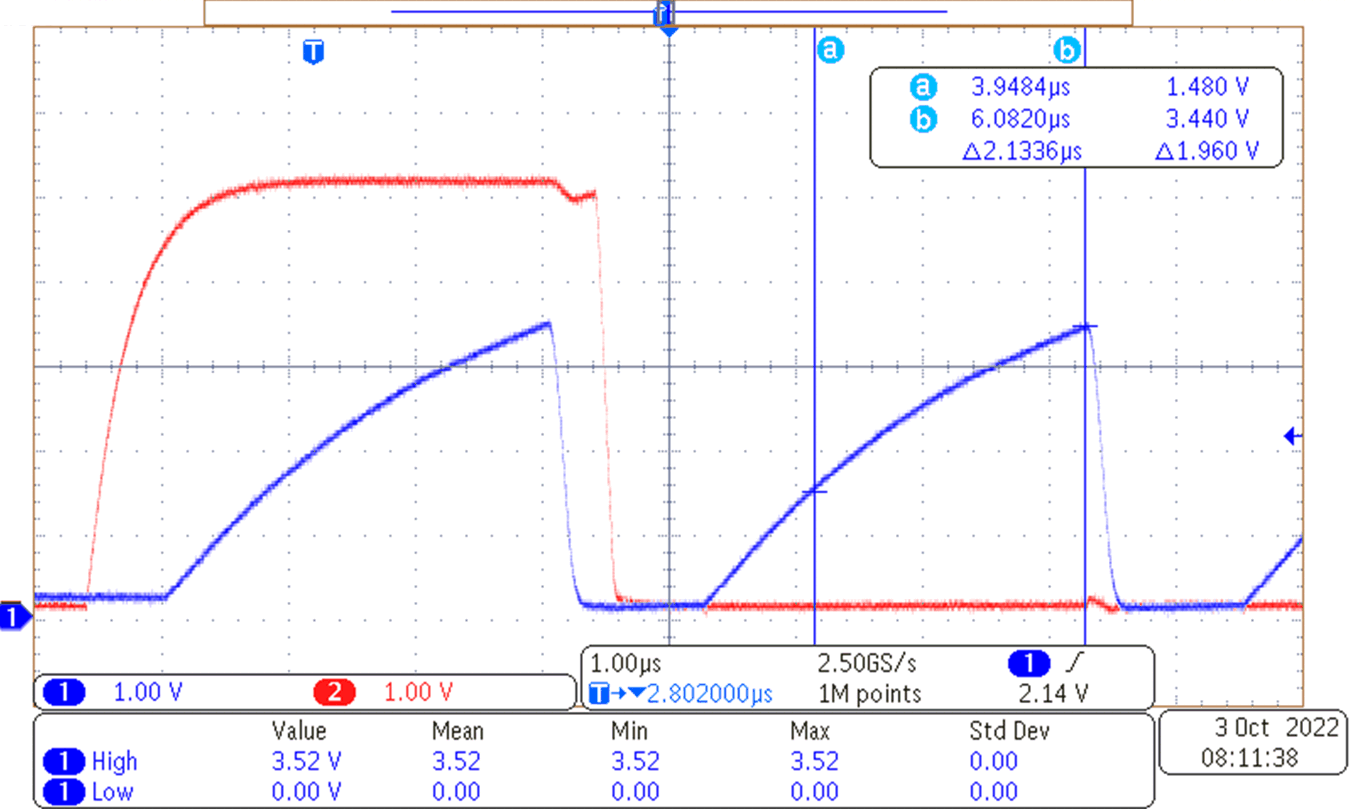

I2C 中的上升时间定义为 I2C 信号从逻辑低电平转换到逻辑高电平所需的时间。I2C 标准中逻辑高电平的最小值定义为 VCC 的 70%;I2C 标准中逻辑低电平的最大值定义为 VCC 的 30%。因此,上升时间的测量值为 I2C 信号从 VCC 的 30% 转换为 VCC 的 70% 的时间。图 3-5 显示了上升转换期间 SDA、SCL 的一个示例。使用示波器测量 I2C 总线上 SDA 和 SCL 线路的上升时间。

图 3-5 上升时间示例

图 3-5 上升时间示例调试 I2C 总线时,应确认上升时间不超过 I2C 总线工作频率的最大上升时间要求(请参阅图 3-5 中的表格),这一点非常重要。如果上升时间超过 I2C 标准所述的限值,可能会导致数据位被无意中从数据传输帧中删除(对于目标中的每个 ACK 位,应该从控制器发送 8 位)。总线电容和上拉电阻都是可能影响上升时间的因素,因此每当遇到上升时间超出允许限制的问题时,请检查这两个参数(有关如何使用上拉电阻和电容来计算上升时间的更多信息,请参阅 I2C 总线上拉电阻计算 应用手册)。

图 3-6 显示了上升时间超过 I2C 标准所规定最大值的示例。

图 3-6 超出规格范围的上升时间示例

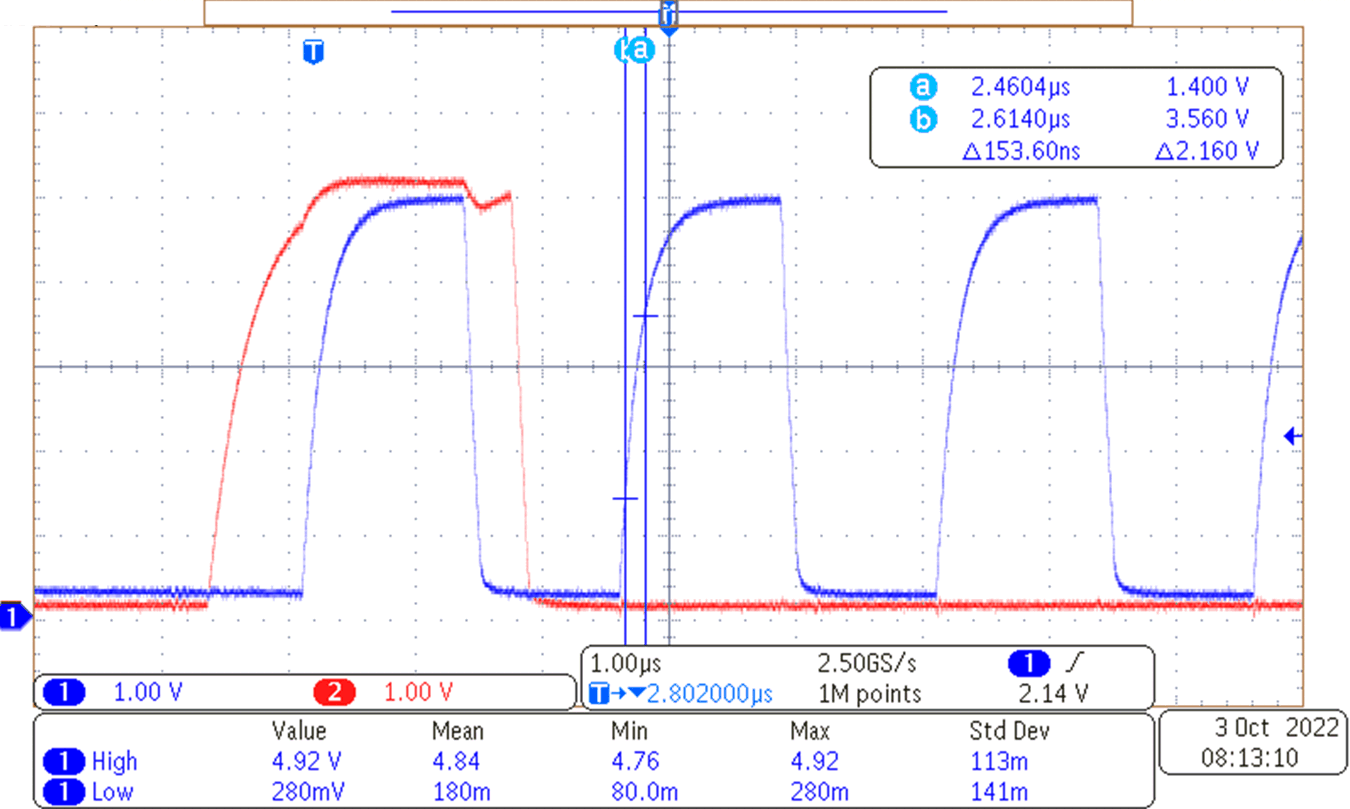

图 3-6 超出规格范围的上升时间示例图 3-7 显示了上升时间符合 I2C 标准的示例。

图 3-7 处于规格范围内的上升时间示例

图 3-7 处于规格范围内的上升时间示例