ZHCACT4 june 2023 AM2431 , AM2432 , AM2434 , AM2631 , AM2631-Q1 , AM2632 , AM2632-Q1 , AM2634 , AM2634-Q1 , AM263P2 , AM263P4 , AM263P4-Q1 , AM3351 , AM3352 , AM3354 , AM3356 , AM3357 , AM3358 , AM3358-EP , AM3359 , AM4372 , AM4376 , AM4377 , AM4378 , AM4379 , AM5706 , AM5708 , AM5716 , AM5718 , AM5718-HIREL , AM5726 , AM5728 , AM5729 , AM5746 , AM5748 , AM5749 , AM6411 , AM6412 , AM6421 , AM6422 , AM6441 , AM6442 , AM6526 , AM6528 , AM6546 , AM6548

3.1 PRU CRC16/32 模块

通信帧封装中需要进行循环冗余校验 (CRC),以确保数据传输过程中的数据准确性。每个 PRU 内核都有一个指定的外设 CRC16/32 模块,为通信系统提供错误检测功能。CRC16/32 模块支持具有不同多项式的 CRC32、CRC16 和 CRC16-CCITT 功能。该模块还通过使用 PRU 宽边接口与 PRU 内部寄存器 R25 至 R29 连接。R29 映射到 CRC_DATA 寄存器,支持最大 32 位数据宽度,并根据配置以 16 位或 32 位读回检查数据。可以生成具有 16 位数据字的 16 位 CRC 数据,并将其放入每个帧中。图 3-1 显示了 PRU CRC16/32 模块的方框图,以下代码显示了用于 16 位数据的 CRC16 函数:

zero &r25, 4 ; config CRC type

xout CRC_XID, &25, 4 ; enable CRC module, CRC_XID = 0x1

mov r29, r20 ; load CRC data, ASCII equivalent for "21"

xout CRC_XID, &29.w0, 2 ; push CRC data to CRC16 module

nop

xin CRC_XID, &r28, 4 ; load the accumulated CRC result into PRU 图 3-1 PRU CRC16/32 模块方框图

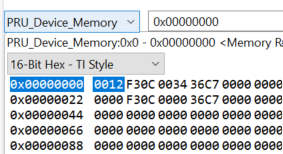

图 3-1 PRU CRC16/32 模块方框图CRC 输入数据必须交换字节,因为 PRU 基于最低有效字节 (LSByte) 优先架构。例如,必须将 0x3412 作为输入数据给出,才能对 0x1234 执行 CRC16。图 3-2 显示了 CRC16/32 模块的验证结果。PRU0 从 PRU1 GPO 每 16 位接收一次数据,并存储在 PRU DRAM 中从 0x00000000 开始的地址中。

基地址存储 PRU1 GPO 发送的原始数据 (0x12)。接收到的数据被发送到 PRU0 CRC 模块,并将累积的 CRC 结果加载到 PRU0 R28 寄存器和偏移量为 0x24 的存储器地址中。偏移量为 0x02 的存储器地址存储来自 PRU1 的数据 0x12 的 CRC16 结果 (0xf30c)。地址偏移 0x04 存储 PRU1 GPO 发送的原始数据 (0x34)。接收到的数据被发送到 PRU0 CRC 模块,并将累积的 CRC 结果加载到 PRU0 R28 寄存器和偏移量为 0x26 的存储器地址中。偏移量为 0x06 的存储器地址存储来自 PRU1 的数据 0x34 的 CRC16 结果 (0x36c7)。图 3-2 表明,从存储器值来看,原始数据和 CRC 数据都是正确的。

图 3-2 PRU CRC16 模块验证

图 3-2 PRU CRC16 模块验证