ZHCACV9 july 2023 PCM3120-Q1 , PCM5120-Q1 , PCM6120-Q1 , TLV320ADC5120

4.10 I2C 列表

电容式麦克风:单端直流耦合输入

下面的电路是直流耦合电容式麦克风的电路。本设计设置了 3.3V 的 MicBias,并使用 3k 的偏置电阻器在 INxP 引脚上设置 1.375V 的静态直流电平。AVDD 为 3.3V。麦克风拾取的声音信号会在这个静态直流偏置上产生变化。

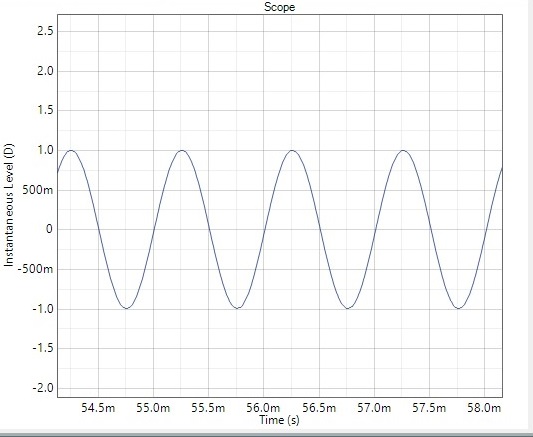

高通滤波器用于从数字输出中消除静态直流电平。下面显示的数字输出捕获是在 1.375V 直流偏置上波动的 1Vrms 输入信号。

图 4-18 单端直流耦合麦克风电路

图 4-18 单端直流耦合麦克风电路 图 4-19 数字输出捕获 (Vin = 1VRMS)

图 4-19 数字输出捕获 (Vin = 1VRMS)Input Timing: 32 bit TDM, FSYNC = 48-kHz, BCLK = 12.288 Mhz.

w 9c 00 00 # Select Page 0

w 9c 01 01 # Reset Device

# 1mS Delay.

w 9c 00 00 # Select Page 0

w 9c 02 81 # Wake up and Enable AREG

w 9c 05 15 # ASI Channel configuration

w 9c 0c 01

w 9c 0d 02

w 9c 0e 03

w 9c 3b 60 # MicBias = 3.3 V

w 9c 3c b4 # Channel 1 configuration

w 9c 41 b4 # Channel 2 configuration

w 9c 74 c0 # input and output Configuration

# High pass filter coefficients

w 9c 49 e6

w 9c 4a 48

w 9c 4b c6

w 9c 4c 80

w 9c 4d 19

w 9c 4e b7

w 9c 4f 3a

w 9c 50 7f

w 9c 51 cc

w 9c 52 91

w 9c 53 8b

w 9c 00 06 # Select page 6

w 9c 1d 04

w 9c 1e b0

w 9c 7e 2d

w 9c 00 00 # Power up/down

w 9c 75 E0电容式麦克风:差分直流耦合输入

下面的电路是差分直流耦合电容式麦克风的电路。本设计设置了 3.3V 的麦克风偏置,并使用 1.1K 的偏置电阻器 R 在 INxP 引脚上设置 2.25V 的静态直流电平,在 INxM 引脚上设置 0.75V 的静态直流电平。AVDD 为 3.3V。麦克风拾取的声音信号会在这些静态直流偏置电平上产生变化。

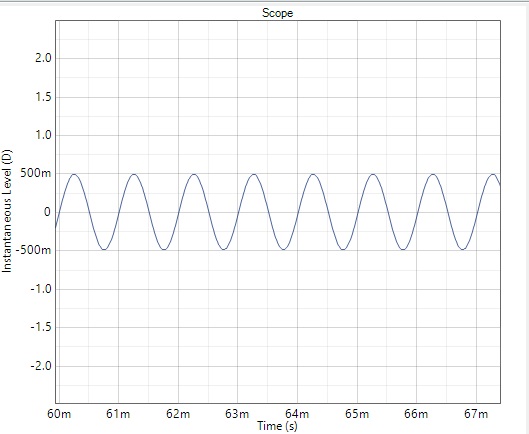

高通滤波器用于从数字输出中消除静态直流电平。下面显示的数字输出捕获适用于 1Vrms 差分输入。

图 4-20 电容式麦克风的差分直流耦合电路

图 4-20 电容式麦克风的差分直流耦合电路 图 4-21 数字捕获(1Vrms 的模拟差分输入)

图 4-21 数字捕获(1Vrms 的模拟差分输入)Input Timing: 32 bit TDM, FSYNC = 48-kHz, BCLK = 12.288 Mhz.

w 9c 00 00 #Select Page 0

w 9c 01 01 # Reset Device

# 1mS Delay

w 9c 00 00 # Select Page 0

w 9c 02 81 # Wake up and Enable AREG

w 9c 05 15

w 9c 0c 01 # ASI Channel configuration

w 9c 0d 02

w 9c 0e 03

9c 3b 60 # MicBias = 3.3 V

w 9c 3c 90 # Channel 1 configuration

w 9c 41 90 # Channel 2 configuration

w 9c 74 c0 # input and output Configuration

w 9c 00 04 # Select page 4

# High pass filter coefficients

w 9c 49 e6

w 9c 4a 48

w 9c 4b c6

w 9c 4c 80

w 9c 4d 19

w 9c 4e b7

w 9c 4f 3a

w 9c 50 7f

w 9c 51 cc

w 9c 52 91

w 9c 53 8b

w 9c 00 06 # Select page 6

w 9c 1d 04

w 9c 1e b0

w 9c 7e 2d

w 9c 00 00 # Select page 0

w 9c 75 E0