ZHCACX7 july 2023 LP5890 , LP5891 , TLC6983 , TLC6984

2.2 设计扫描线数

图 2-1 显示了 DS-PWM 算法,其中有 32 条线集成到 TLC6983 中。帧速率 (fframe_rate)、段长 (NGCLK_seg)、GCLK 频率 (fGCLK)、线路开关时间 (TSW)、扫描线数 (Nscan_line)、子周期(或子帧)数 (Nsub_period) 和一帧中的消隐时间 (Tblank) 如下所示。

图 2-1 具有 32 条扫描线的 DS-PWM 算法

图 2-1 具有 32 条扫描线的 DS-PWM 算法允许的最大 GCLK 频率 (fGCLK) 为 160MHz。允许的最短线路开关时间 TSW 可设置为 45 GCLK。不过,建议线路切换时间至少为 1μs 至 1.5μs。在理想配置中,消隐时间 (Tblank) 等于 0。因此,允许的扫描线数上限为:

使用方程式 4 计算出的结果为 19,远小于节 1中讨论的 32 条扫描线,双 TLC6983 在可堆叠模式下可支持 32 条扫描线。此结果意味着实际可用扫描线数上限受限于米6体育平台手机版_好二三四所需的最大 PWM 分辨率以及驱动器本身生成的最大 GCLK 频率。重申一下,在 GCLK 频率有限的情况下,同时实现非常高的 PWM 分辨率和高扫描线数非常困难。需要在 PWM 分辨率与扫描线数之间进行权衡。集成密度越高(扫描线数越多),PWM 分辨率越低。例如,考虑将分辨率从 16 位降低到 15 位的影响。不能降低 PWM 分辨率,否则会降低显示效果,而必须减少扫描线数。正是由于这种权衡,才使得市场上的米6体育平台手机版_好二三四能够拥有支持 16 位或更高位的驱动器,但“实际”16 位 PWM 分辨率要低得多。此外,也正是由于这种关系,才使得市场上一些高端米6体育平台手机版_好二三四虽然具有非常少的扫描线数,却能获得出色的显示效果(从 16 位、20 位或更高的 PWM 分辨率)。

回到设计要求,LED 面板模块 (96 × 108) 有 96 列;可堆叠模式(子块)下的双 TLC6983 可支持 32 × 32 RGB 像素(32 个 RGB 通道和 32 条扫描线)。因此,所有 RGB 通道都可以得到充分利用(96 / 32 = 行中 3 个子块)。对于此用例,建议使用 6 作为级联器件数 (Ncascade) (96 / 16 = 6)。级联数量可以设置得更高,例如 12 个级联器件,但更多级联器件需要更高的 SCLK 频率(SCLK 设计将在后面章节讨论),这会导致 EMI 更差,并且对控制器的 FPGA 也有更高的要求。

对于扫描线,应考虑以下关系:ROUNDUP(108 / 19, 0) = 6,108 / 6 = 18。此计算会得到列中有 6 个子块。108 可被 18 整除,扫描线数 (Nscan_line) 可以设置为 18。如果分子不可整除,则建议尽量将扫描线间隔开,以实现负载共享目的。例如,如果允许的扫描线数上限为 16,该扫描线会表明在一列中 3 个子块有 16 条扫描线,4 个子块有 15 条扫描线。

最小 GCLK 频率的计算公式为:

使用前面的数字,根据此公式计算得到的结果为 147.8MHz。

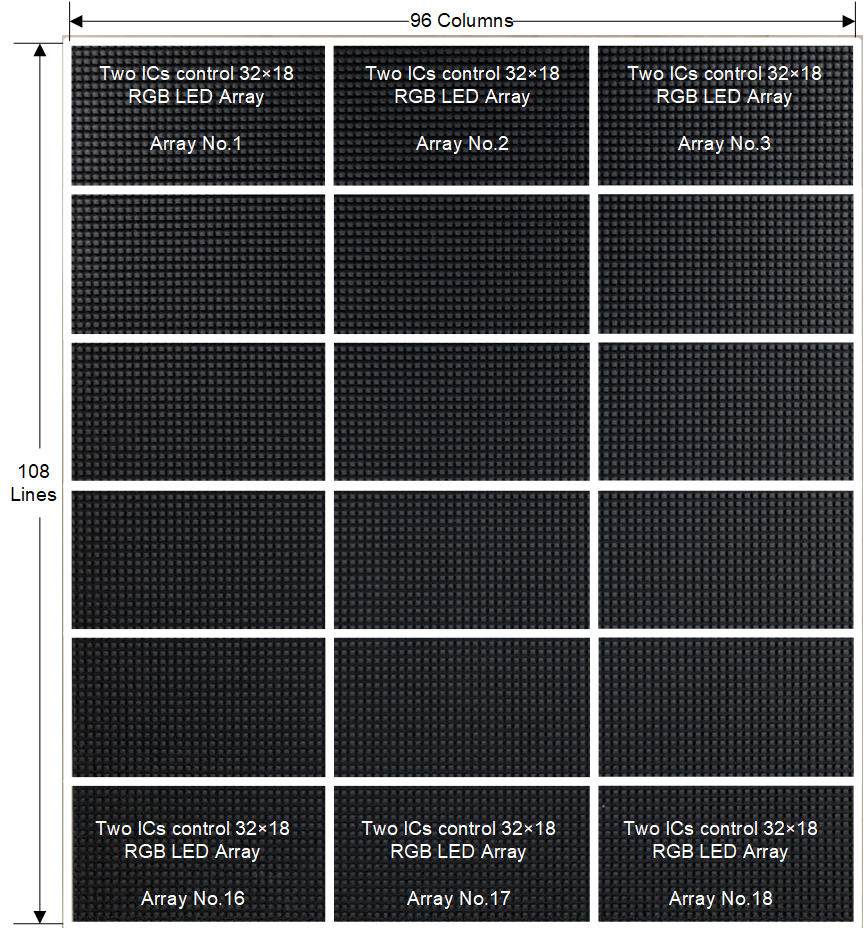

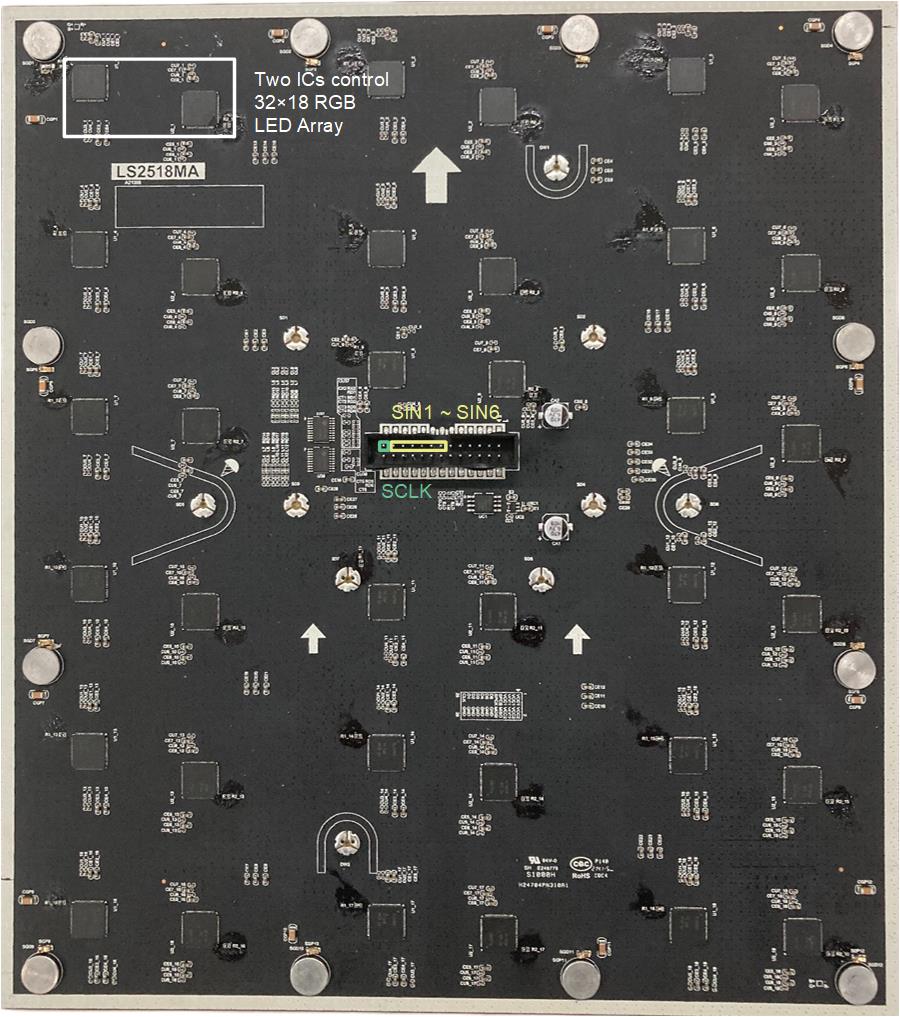

图 2-2 显示了图 1-1 中突出显示的 LED 面板 (96x108) 的更多详细信息。LED 面板模块分解成十八个 32 × 18 子块(每排 6 组)。每个子块都有两个采用可堆叠模式连接的 TLC6983。图 2-3 和图 2-4 展示了物理原型板。

图 2-2 LED 面板模块 (96 × 108) 的详细信息

图 2-2 LED 面板模块 (96 × 108) 的详细信息 图 2-3 LED 面板模块原型板 (96 × 108) 的正面

图 2-3 LED 面板模块原型板 (96 × 108) 的正面 图 2-4 LED 面板模块原型板 (96 × 108) 的背面

图 2-4 LED 面板模块原型板 (96 × 108) 的背面