ZHCAD94 October 2023 MSPM0C1104 , MSPM0L1306

4.2.2 HFCLK_IN

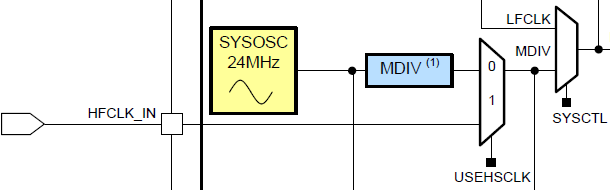

要将 HFCLK 配置为使用数字时钟输入,请先配置 IOMUX 以在相应的引脚上启用 HFCLK_IN 功能。当 IOMUX 配置正确且时钟源正在向 HFCLK_IN 输出时钟时,设置 SYSCTL 内 HSCLKEN 寄存器中的 USEEXTHFCLK 位。

要在选择 HFCLK_IN 作为 HFCLK 源后从 HFCLK_IN 获取 MCLK,请首先设置 HSCLKCFG 寄存器中的 HSCLKSEL 位,以选择 HFCLK 作为高速时钟源。然后,设置 MCLKCFG 寄存器中的 USEHSCLK 位,选择高速时钟源作为 MCLK 源。在设置 USEHSCLK 后,一定不能改变 HSCLKCFG 并且一定不能禁用 HFCLK_IN,直到通过清除 USEHSCLK 并验证已由硬件清除 CLKSTATUS 中的 HSCLKMUX 位来将 MCLK 源切换回 SYSOSC。

HFCLK_IN 与数字方波 CMOS 时钟输入兼容,且推荐的典型占空比为 50%。

图 4-3 MSPM0C 系列外部时钟输入 HFCLK_IN

图 4-3 MSPM0C 系列外部时钟输入 HFCLK_IN