ZHCAD94 October 2023 MSPM0C1104 , MSPM0L1306

9.4 如何选择电路板层和建议堆叠

为了减少高速信号上的反射,必须匹配拉电流、灌电流和传输线路之间的阻抗。信号布线的阻抗取决于其几何形状及其相对于任何参考平面的位置。

针对特定的阻抗要求,差分对之间的布线宽度和间距取决于所选的 PCB 堆叠。由于根据 PCB 技术的类型和成本要求,最小布线宽度和间距存在限制,因此需要选择 PCB 堆叠,来实现所有必需的阻抗。

可使用的最小配置为 2 个堆叠。对于具有多个高速信号且非常密集的 PCB,需要使用 4 层或 6 层电路板。

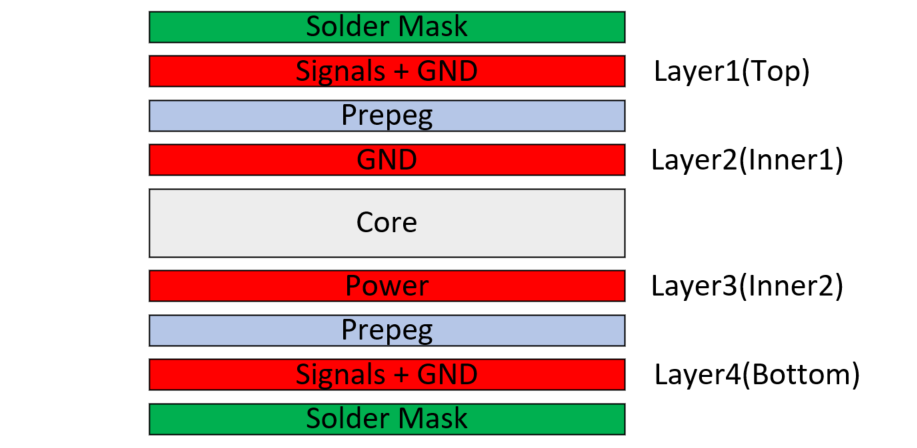

以下堆叠(请参阅图 9-5)是一个 4 层电路板示例,可用作帮助进行堆叠评估和选择的起点。这些堆叠配置使用靠近电源平面的 GND 平面来增加电容并减小 GND 和电源平面之间的间隙。因此,顶层的高速信号将具有一个实心 GND 参考平面,这有助于减少 EMC 辐射,因为增加层数并为每个 PCB 信号层提供 GND 参考将进一步提高辐射 EMC 性能。

图 9-5 四层 PCB 堆叠示例

图 9-5 四层 PCB 堆叠示例如果系统不是很复杂,没有高速信号或一些敏感的模拟信号,那么 2 个堆叠的结构就足够了。