ZHCADE0 October 2023 AM625SIP

10 电源去耦

中优先级接口和配电平面和覆铜将在串行器/解串器接口之后布线。强烈建议在继续使用其他接口之前完成所有串行器/解串器布线。在为串行器/解串器布线执行 PCB 仿真之前,必须放置配电平面和覆铜以及所有去耦,因为这会影响高速接口的返回电流。超高速源同步接口(例如 RGMII 和 QSPI)可能也需要仿真,因此可能也需要在此时完成。

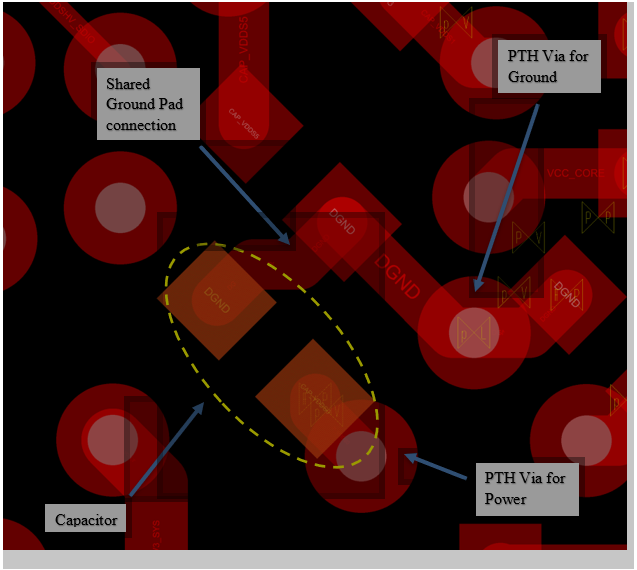

需要特别注意连接到 AM62XSiP 器件上 CAP_VDDS* BGA 引脚的 1uF 输出电容器。这些电容器应尽可能靠近引脚放置,并且在 CAP_VDDS BGA 引脚和电容器上的电源焊盘之间应存在低电感路径。在 AM62XSiP SK EVM 的 CAP_VDDS0 网络上使用的布局如图 10-1 所示。请注意,该电容器的 GND 焊盘与附近的其他电容器共用,这样可以节省布线资源。此外,务必使电容器电源和 GND 焊盘连接的 PTH 过孔尽可能彼此靠近,以更大限度地减小环路电感。

图 10-1 AM62XSiP SK EVM CAP_VDDS0 输出电容器布局

图 10-1 AM62XSiP SK EVM CAP_VDDS0 输出电容器布局如果电容器可以放置在 SoC 正下方,则可以改善这种布局方式。VDD_CORE 电源的去耦电容器也应获得与 CAP_VDDS* 引脚上的去耦电容器相同的优先级,应放置在插座下方,并以极小的电感连接到 AM62XSiP 器件上相应的 BGA 引脚。