ZHCADE7 November 2023 CDCE6214 , CDCE6214-Q1 , CDCE6214Q1TM , LMK00301 , LMK00304 , LMK00306 , LMK00308 , LMK00334 , LMK00334-Q1 , LMK00338 , LMK03318 , LMK03328 , LMK3H0102 , LMK6C , LMK6H , LMKDB1104 , LMKDB1108 , LMKDB1120 , LMKDB1202 , LMKDB1204

3.3 扩频时钟

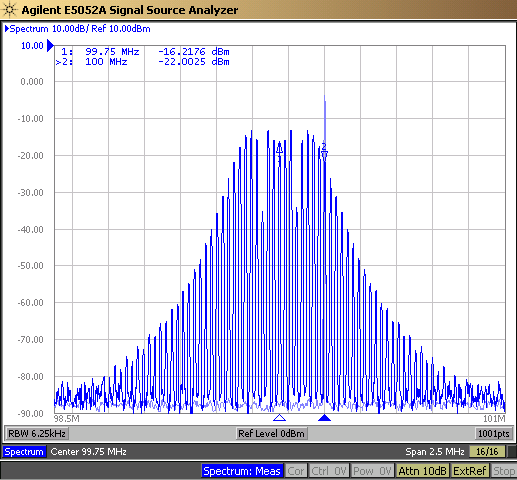

通用时钟和独立参考架构均支持展频时钟。使用 SSC 时,时钟频率被调制,从而将辐射发射分布在多个频率上,而不是单个峰值频率上。这种频率调制会增加抖动。通用时钟 PCIe 系统指定 30kHz 至 33kHz 之间的调制频率,扩展范围在 0% 和 -0.5% 之间,称为向下展频 SSC。对于独立参考架构,扩展范围为 0% 至 -0.3%。图 3-3 展示了不带 SSC 时的峰值能量与带 -0.5% 向下展频 SSC 时的峰值能量之间的差异。-5dB 处的单个 100MHz 峰值适用于不带 SSC 的情况。启用 -0.5% 向下展频 SSC 后,能量峰值为 -14dB。

如果 100MHz REFCLK 具有 -0.5% 向下展频 SSC,PCIe 器件必须能够承受 100MHz 的较大 ppm 变化:在典型频率稳定性预算中为 100ppm,在时钟频率扩展中为 2500ppm。此规格通常表示为 -100ppm 至 +2600ppm。在 SRIS 中,允许的最大向下展频 SSC 为 -0.3%。这种情况下的总频率稳定性为 -100ppm 至 +1600ppm。

图 3-3 不带 SSC 和 -0.5% 向下展频 SSC 时为 100MHz REFCLK

图 3-3 不带 SSC 和 -0.5% 向下展频 SSC 时为 100MHz REFCLK对于通用时钟架构,两个时钟的抖动相同。因此,对于独立参考架构的 SSC,时钟可以是独立基准无展频 (SRNS) 或独立基准独立展频 (SRIS)。使用 SRIS 时,发送器和接收器在任何给定时间的时钟频率都不同。在这种情况下,两个 PCIe 器件都会通过实现缓冲器来解决时钟频率差异问题。