ZHCADH3 December 2023 MSPM0C1103 , MSPM0C1103-Q1 , MSPM0C1104 , MSPM0C1104-Q1 , MSPM0G1105 , MSPM0G1106 , MSPM0G1107 , MSPM0G1505 , MSPM0G1506 , MSPM0G1507 , MSPM0G1519 , MSPM0G3105 , MSPM0G3105-Q1 , MSPM0G3106 , MSPM0G3106-Q1 , MSPM0G3107 , MSPM0G3107-Q1 , MSPM0G3505 , MSPM0G3505-Q1 , MSPM0G3506 , MSPM0G3506-Q1 , MSPM0G3507 , MSPM0G3507-Q1 , MSPM0G3519 , MSPM0L1105 , MSPM0L1106 , MSPM0L1117 , MSPM0L1227 , MSPM0L1228

3.6.1.1 MSPM0 的中断管理

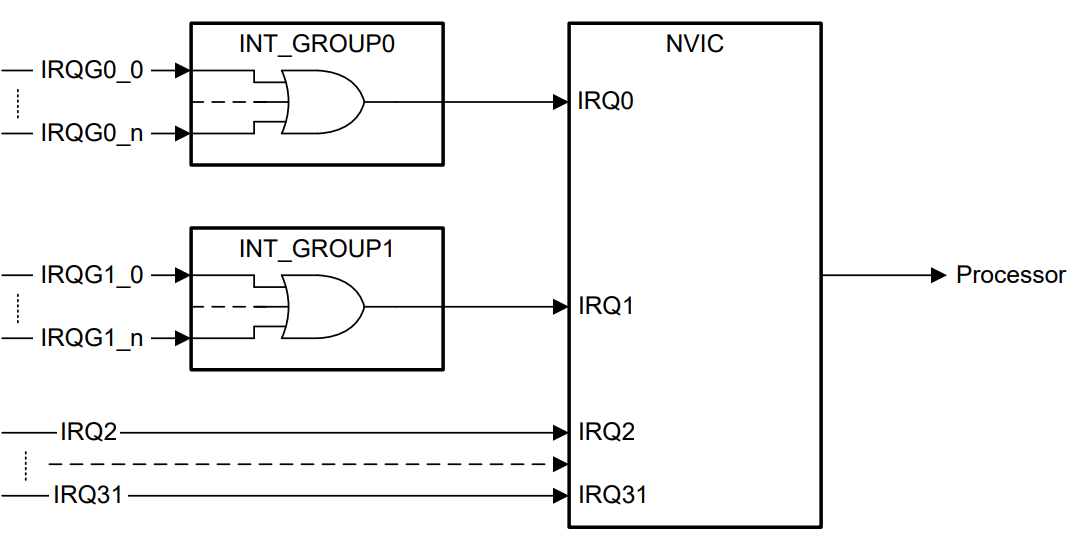

MSPM0 器件通过 NVIC 中的 IPRx 寄存器设置每个外设中断源的优先级,并通过 NVIC 中的 ISER 和 ICER 寄存器屏蔽/取消屏蔽外设中断源。每个外设中断都包含各种中断条件。例如,作为外设中断源,UARTx 有多个中断条件,例如发送中断和接收中断等。中断条件由外设端的六个标准寄存器进行管理。图 3-2 显示了外设中断层次结构。

图 3-2 MSPM0 的外设中断层次结构

图 3-2 MSPM0 的外设中断层次结构