ZHCADI5 December 2023 DP83869HM

2.6.1 RGMII

参考本节中的波形,验证移位和对齐模式下 RGMII 的预期 MAC 数据和时钟信号。要捕获数据和时钟信号,请在靠近接收器端的位置进行测量请注意以下有关选择正确延迟模式的要求:

表 2-6 选择正确的 RGMII 延迟模式

| 如果 MAC 的配置为: | 所需的 PHY 配置 |

|---|---|

| TX 端的 RGMII 对齐模式 | TX 端的 RGMII 移位模式 |

| RX 端的 RGMII 对齐模式 | RX 端的 RGMII 移位模式 |

| TX 端的 RGMII 移位模式 | TX 端的 RGMII 对齐模式 |

| RX 端的 RGMII 移位模式 | RX 端的 RGMII 对齐模式 |

RX_D[3:0] 数据与 RX_CLK 对齐

对于在 RX 对齐模式下设置为 10/100Mbps 的 PHY,探测 MAC 端的时钟和数据信号,并与下图的参考波形进行比较。

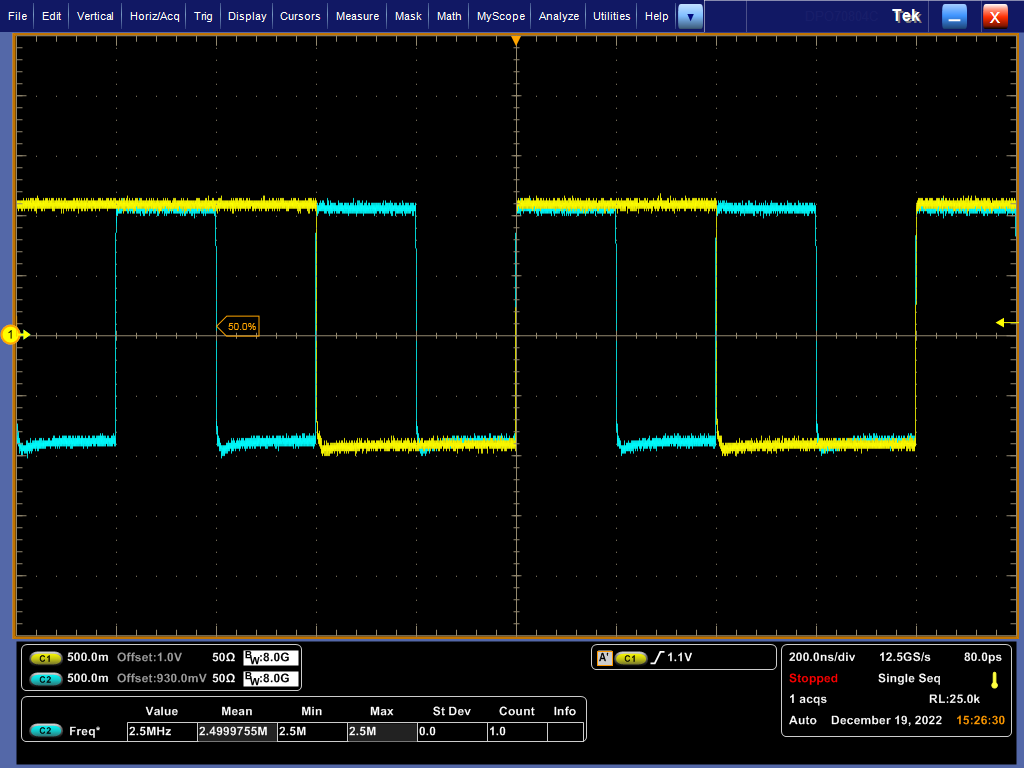

图 2-10 10Mbps 数据与 RX_CLK 对齐

图 2-10 10Mbps 数据与 RX_CLK 对齐验证时钟 (C2) 的频率是否为 2.5MHz,以及在时钟的上升沿对数据 (C1) 进行采样。

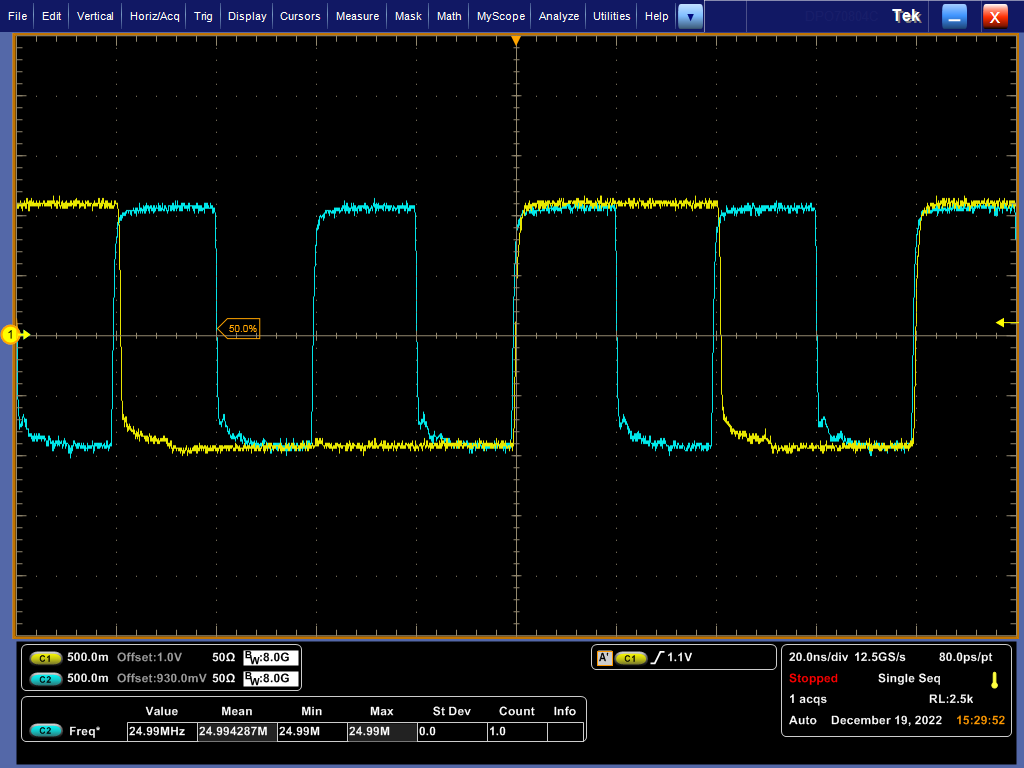

图 2-11 100Mbps 数据与 RX_CLK 对齐

图 2-11 100Mbps 数据与 RX_CLK 对齐验证时钟 (C2) 的频率是否为 25MHz,以及在时钟的上升沿对数据 (C1) 进行采样。

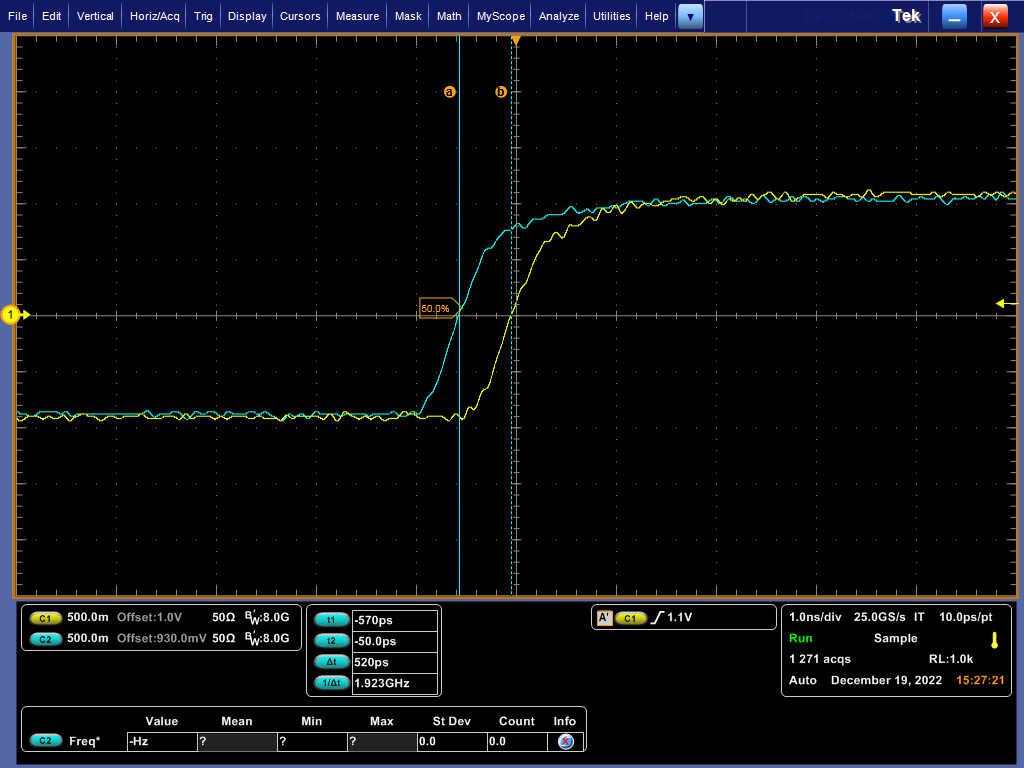

图 2-12 对齐模式下的 10Mbps 数据和时钟延迟

图 2-12 对齐模式下的 10Mbps 数据和时钟延迟验证对齐模式下时钟和数据之间的延迟是否小于 500ps。

移位模式下的 RX_D[3:0] 数据和 RX_CLK

对于在 RX 移位模式 (0x32) 下设置为 10/100Mbps 的 PHY,探测 MAC 端的时钟和数据信号,并与下面的参考波形进行比较。

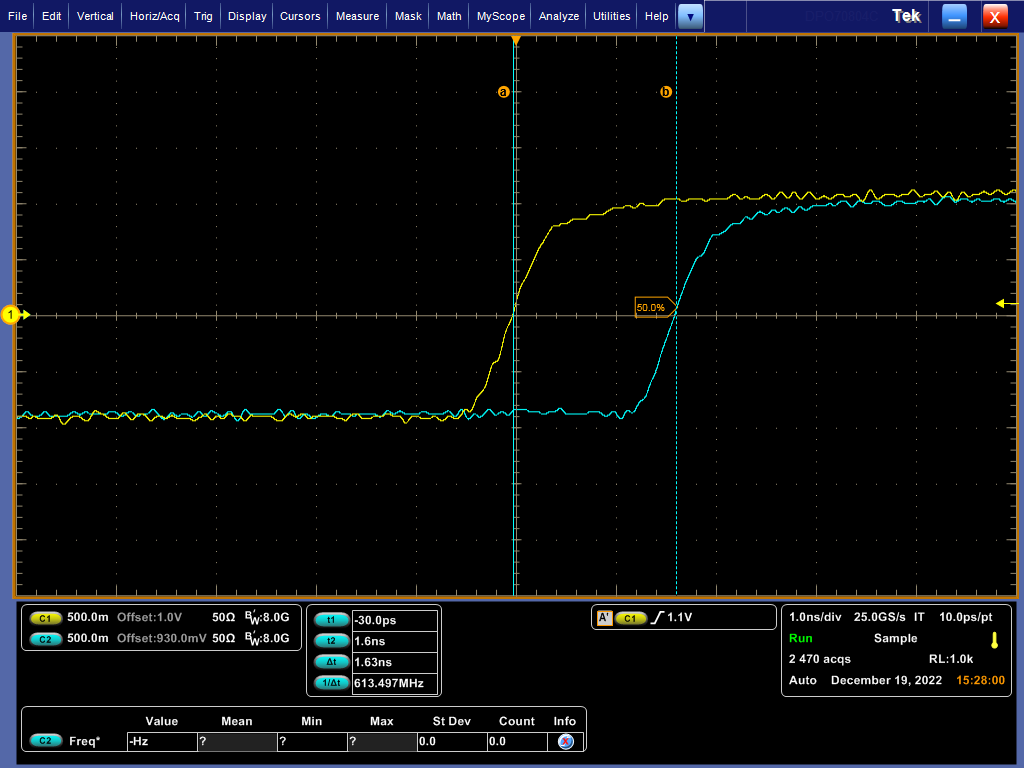

图 2-13 移位模式下的 10Mbps 数据和 RX_CLK(4ns 编程延迟)

图 2-13 移位模式下的 10Mbps 数据和 RX_CLK(4ns 编程延迟)验证移位模式下时钟和数据之间的延迟是否大于 1ns。编程的延迟是相对于时钟在对齐模式下的初始位置。在设置移位模式之前和之后测量时钟位置的差值将得到一个更接近编程延迟的值。

移位和对齐模式下为 TX_D[3:0] 和 TX_CLK

对于在 TX 移位或对齐模式下设置的 PHY,探测 PHY 端的数据和时钟信号,并验证是否满足以下时序要求:

| 参数 | 最小值 | 标称值 | 最大值 | 单位 | |

|---|---|---|---|---|---|

| TskewT | 数据到时钟输出偏斜 (在变送器处) |

–500 | 0 | 500 | ps |

| TskewR | 数据到时钟输入偏斜 (在接收器处) |

1 | 1.8 | 2.6 | ns |

| TsetupT | 数据到时钟输出设置 (在变送器处 – 内部延迟) |

1.2 | 2 | ns | |

| TholdT | 时钟到数据输出保持 (在变送器处 - 内部延迟) |

1.2 | 2 | ns | |

| TsetupR | 数据到时钟输入设置 (在接收器处 – 内部延迟) |

1 | 2 | ns | |

| TholdR | 时钟到数据输入保持 (在接收器处 - 内部延迟) |

1 | 2 | ns | |

| Tcyc | 时钟周期时长 | 7.2 | 8 | 8.8 | ns |

| Duty_G | 千兆位的占空比 | 45 | 50 | 55% | |

| Duty_T | 10/100T 的占空比 | 40 | 50 | 60% | |

| TR | 上升时间(20% 至 80%) | 0.75 | ns | ||

| TF | 下降时间(20% 至 80%) | 0.75 | ns | ||