ZHCADI7A January 2016 – December 2023 DP83822H , DP83822HF , DP83822I , DP83822IF , DP83825I , DP83826E , DP83826I

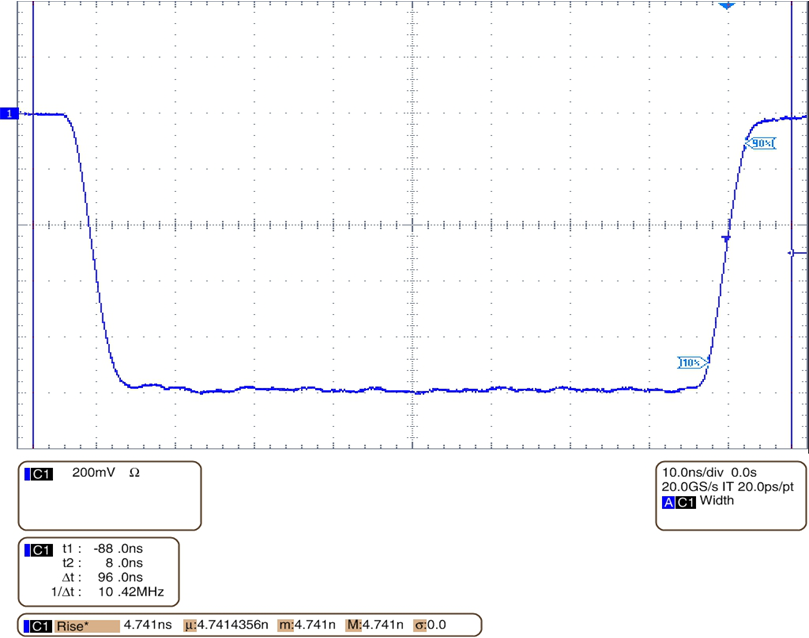

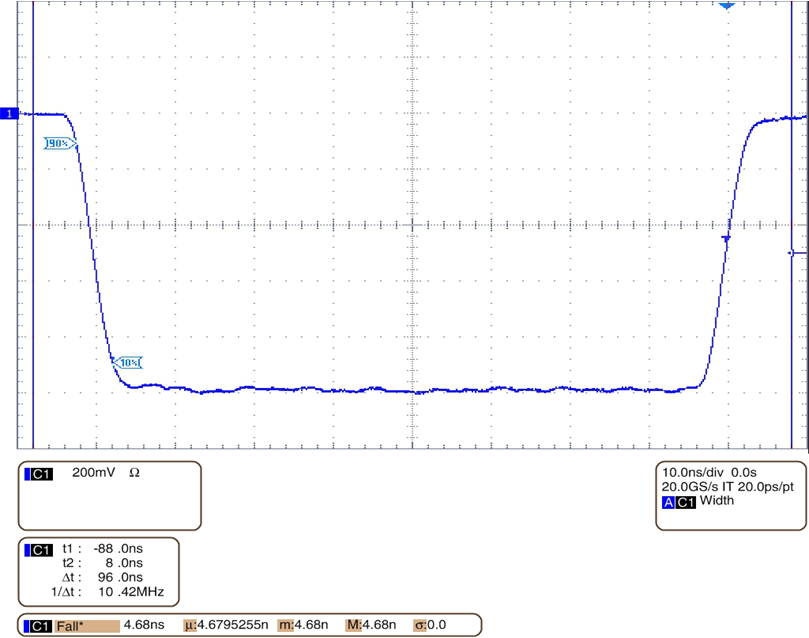

3.2.3 上升和下降时间

目的:确保器件的上升和下降时间在指定范围内。

通过条件:上升和下降时间(正负电压电平都在 10% 到 90% 之间)必须在 3ns 到 5ns 之间。最大和最小上升和下降时间必须在 0.5ns 以内。

图 3-4 100BASE-TX 上升时间示例波形

图 3-4 100BASE-TX 上升时间示例波形 图 3-5 100BASE-TX 下降时间示例波形

图 3-5 100BASE-TX 下降时间示例波形