ZHCADI9 December 2023 TMS320F280023C , TMS320F280025C , TMS320F280025C-Q1 , TMS320F280037C , TMS320F280037C-Q1 , TMS320F280039C , TMS320F280039C-Q1 , TMS320F280049C , TMS320F280049C-Q1 , TMS320F28377D , TMS320F28377D-EP , TMS320F28377D-Q1 , TMS320F28377S , TMS320F28377S-Q1 , TMS320F28379D , TMS320F28379D-Q1 , TMS320F28379S , TMS320F28P650DK

4 关断延迟配置

在谐振模式下,开关频率大于谐振频率,在初级侧 PWM 关闭后,SR MOSFET 上的电流仍然存在,如图 1-1 所示。通过增加关断延迟(通常在 200ns 以内)来延长 SR PWM 的导通时间有助于提高系统效率。为了添加关断延迟,此报告提供了两种配置。

第一个配置选项是利用来自另一个 CLB 逻辑块(如 CLB3)的额外计数器 2。

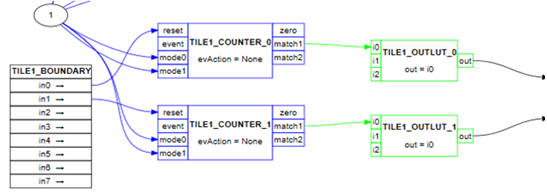

此配置的第一步是设置 CLB 输入 IN0 和 IN1,以使用 EPWM1A 和 EPWM1B 的下降沿将相关计数器复位为 0(图 4-1),并设置匹配 1 值以表示 SR PWM 所需的关断延迟。下一步是选择计数器 2 的匹配 1 事件作为输出,分别替换原来的 CLB2 IN0(EPWM1A 的下降沿)和 IN2(EPWM1B 的下降沿)。

图 4-1 带 2 个额外计数器的第一个 CLB 配置选项

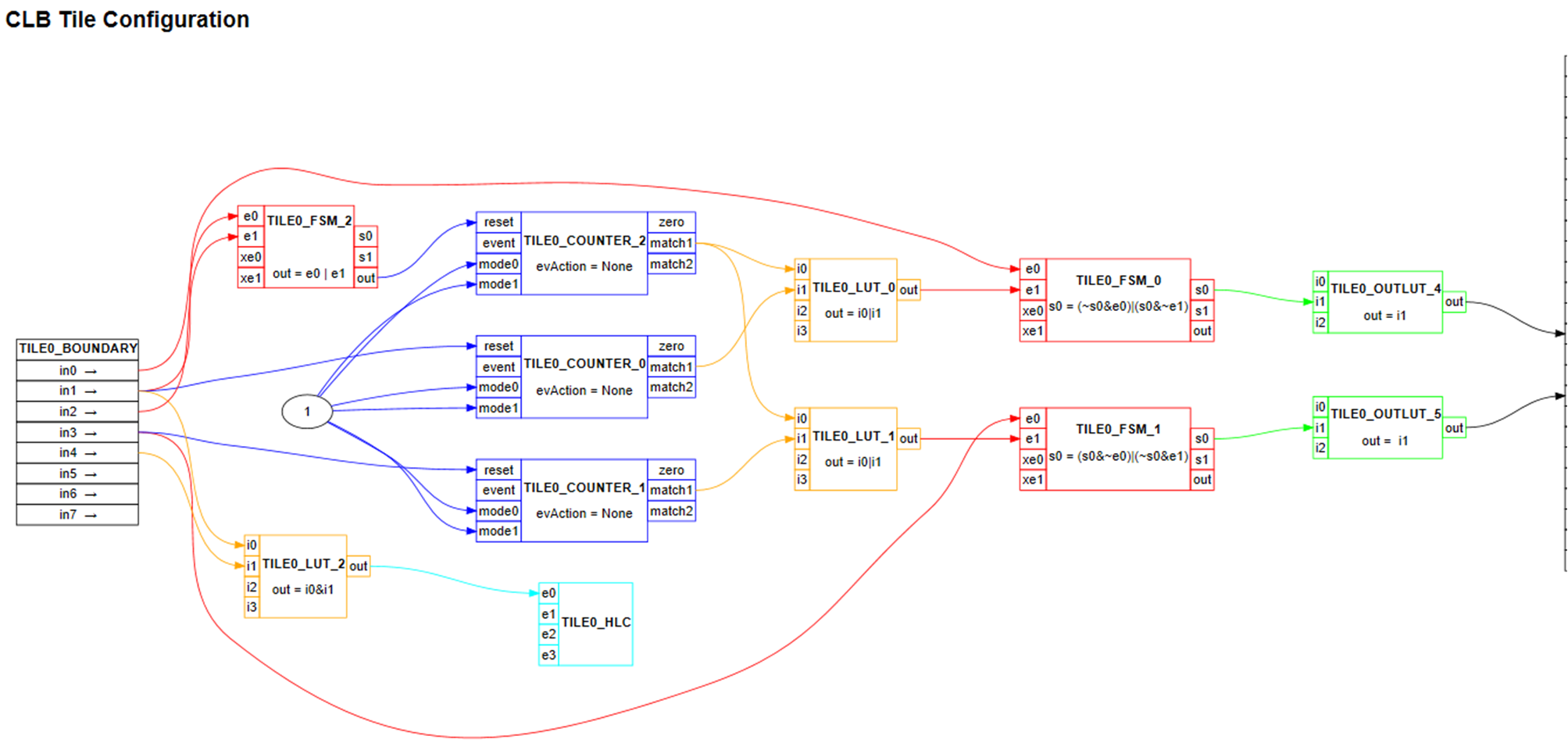

图 4-1 带 2 个额外计数器的第一个 CLB 配置选项对于三相交错 LLC,没有足够的 CLB 逻辑块为关断延迟设计提供额外的计数器(图 4-1);然而,可以使用第二个选项,该选项在同一 CLB 逻辑块内为特定的 SR PWM 使用单个计数器。在第二个选项(图 4-2)中,选择 EPWM1A 和 EPWM1B 的下降沿(与 LUT 的或逻辑),以在使用预期的延迟时间设置匹配 1 值时复位计数器 2。CLB 方框图的重要变化是将 LUT0 和 LUT1 的 IN0 输入替换为计数器 2 的匹配 1 事件。通过该选项,剩余的 FSM 2 将用作 LUT 功能,因为所有三个 LUT 功能均已占用。

图 4-2 具有单个计数器的第二个 CLB 配置选项

图 4-2 具有单个计数器的第二个 CLB 配置选项