ZHCADJ6B November 2023 – January 2024 AM62P , AM62P-Q1

10 DDR 接口

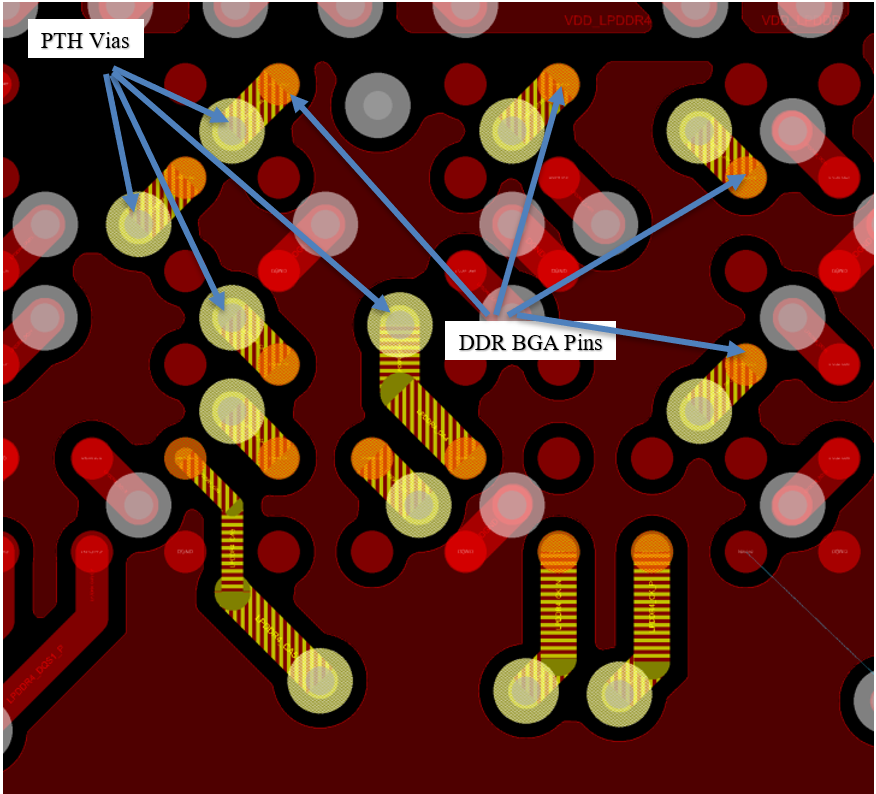

AM62Px 支持连接 LPDDR4 器件。DDR 信号的布线必须具有最高优先级。有关 DDR 布线的详细建议,请参阅 DDR 布线指南文档。下图展示了 AM62Px 板上 DDR 接口的 BGA 分线。

DDR SDRAM 存储器器件通常采用以下布局:数据组焊球最靠近 AM62Px 器件。封装 BGA 焊球图经过精心规划,将 DDR 地址和命令信号放置在数据字节通道 0/1 和数据字节通道 2/3 之间。

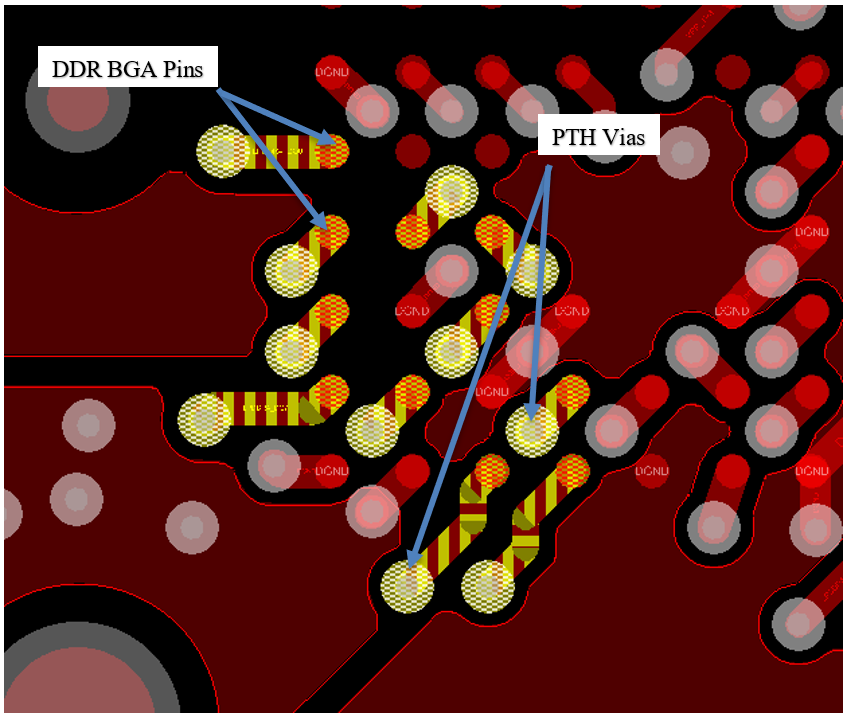

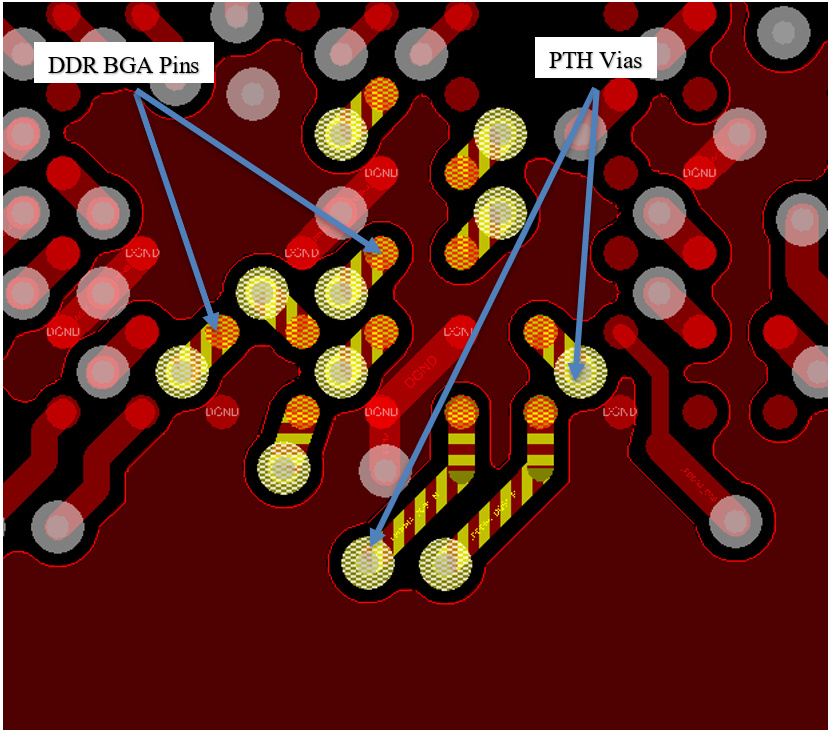

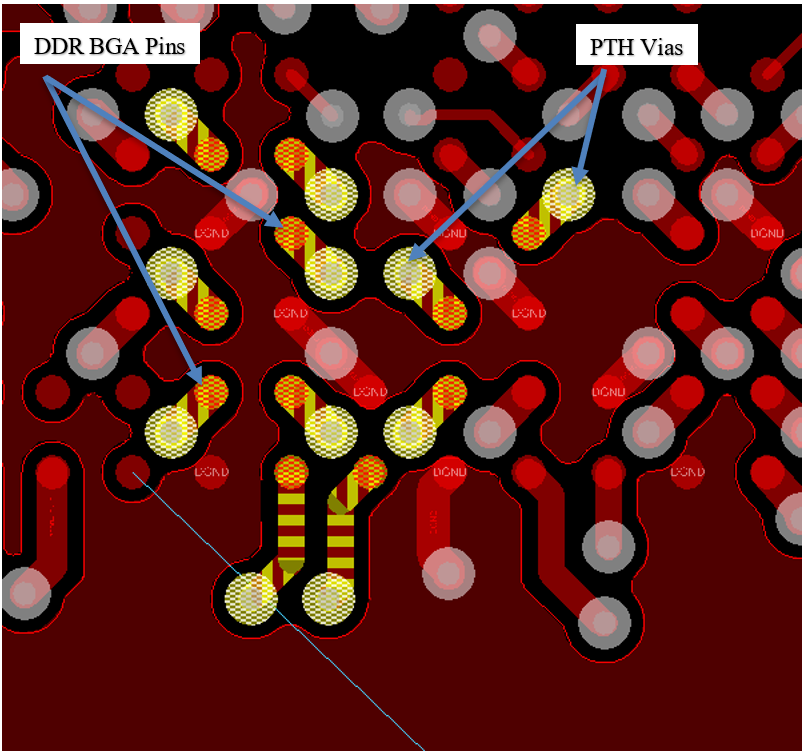

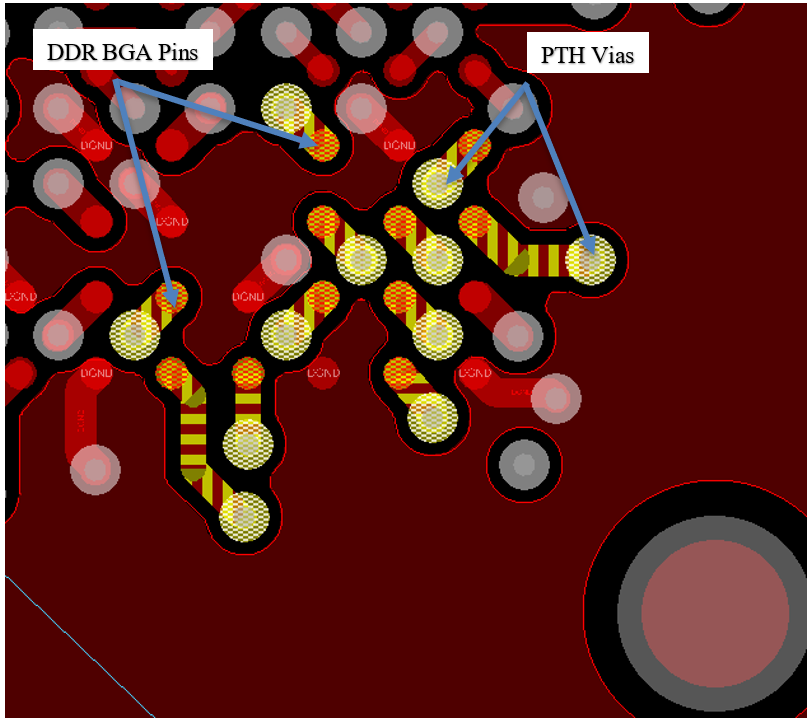

图 10-1 和图 10-2 分别展示了如何迂回 DDR 字节通道 0 和 1。使用电镀穿孔 (PTH) 过孔使得这些信号可以在任何层上在 SoC 和 SDRAM 之间布线。同样,图 10-3 和图 10-4 分别展示了 DDR 字节通道 2 和 3 的迂回。

图 10-1 DDR 字节通道 0 迂回

图 10-1 DDR 字节通道 0 迂回 图 10-2 DDR 字节通道 1 迂回

图 10-2 DDR 字节通道 1 迂回 图 10-3 DDR 数据字节通道 2 迂回

图 10-3 DDR 数据字节通道 2 迂回 图 10-4 DDR 数据字节通道 3 迂回

图 10-4 DDR 数据字节通道 3 迂回地址、命令和时钟信号直接布线到存储器器件。

顶部和内层用于地址和命令信号的迂回和布线。布线长度必须匹配,以确保信号同时到达存储器。SoC 与寄存器引脚之间的长度匹配必须单独进行,并且必须包括内存焊盘的存根和所有过孔长度。有关 DDR 布线的详细建议,请参阅 DDR 布线指南文档。

图 10-5 DDR 地址/命令迂回

图 10-5 DDR 地址/命令迂回这些层上的地址和命令信号的迂回如图 10-5 所示。

地址信号直接从 SoC 布线到存储器器件相关焊盘旁边的过孔。这要求地址信号以正确的顺序迂回。每个地址和命令信号都需要具有相同数量的过孔。使用电镀穿孔 (PTH) 过孔可以灵活地在任何层上进行地址/命令信号布线。