ZHCADM8A October 2023 – May 2024 TAA5212 , TAA5242 , TAC5111 , TAC5112 , TAC5142 , TAC5211 , TAC5212 , TAC5242

1 引言

TAC5212 是一款具有双通道模数转换器的编解码器,其输入引脚(IN1P/M 和 IN2P/M)可配置为差分输入、单端输入或单端多路复用器输入(采用交流或直流耦合)。通过 ADC_CH1_INSRC 配置输入类型,通过 ADC_CH1_IMP 配置输入阻抗,通过 ADC_CH1_CM_TOL 配置耦合和共模容差。

表 1-1 输入配置选择

| 输入配置设置 | B0_P0_R80 (ADC_CH1_CFG0) [7:6] | 输入通道配置 |

|---|---|---|

| 0 | ADC_CH1_INSRC=[00] | 模拟差分输入 |

| 1 | ADC_CH1_INSRC=[01] | 模拟单端输入 |

| 2 | ADC_CH1_INSRC=[10] | 模拟单端多路复用器 INP1 输入 |

3 | ADC_CH1_INSRC=[11] | 模拟单端多路复用器 INM1 输入 |

表 1-2 ADC 输入阻抗选择

| 输入阻抗设置 | B0_P0_R80 (ADC_CH1_CFG0) [5:4] | ADC 通道 1 输入阻抗 |

|---|---|---|

| 0 | ADC_CH1_IMP=[00] | 典型 5kΩ 输入阻抗(对于 4Vrms 情况,为 10kΩ) |

| 1 | ADC_CH1_IMP=[01] | 典型 10kΩ 输入阻抗 |

| 2 | ADC_CH1_IMP=[10] | 典型 40kΩ 输入阻抗 |

| 3 | ADC_CH1_IMP=[11] | 保留 |

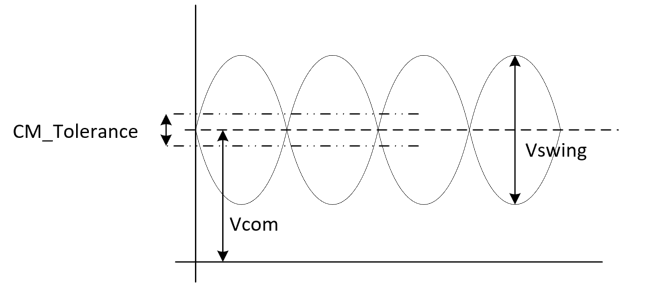

共模容差定义为差分放大器共模信号的变化,如图 1-1中所示。

图 1-1 共模容差

图 1-1 共模容差在交流耦合模式下,该器件系列支持三种共模容差:差分 100mVpp、1Vpp 和轨到轨(电源至地);在直流耦合模式下,它支持差分 1Vpp 和轨到轨(电源至地)。需要根据最大预期共模变化来选择该共模容差。由于较宽的共模容差的确会降低其他性能参数,因此建议选择可能的更低容差模式。

表 1-3 共模容差选择

| 共模容差设置 | B0_P0_R80 (ADC_CH1_CFG0) [3:2] | 输入通道共模容差 |

|---|---|---|

| 0 | ADC_CH1_CM_TOL=[00] | 具有共模变化容差的交流耦合输入,单端配置支持 50mVpp,差分配置支持 100mVpp |

| 1 | ADC_CH1_CM_TOL=[01] | 具有共模变化容差的交流耦合/直流耦合输入,单端配置支持 500mVpp,差分配置支持 1Vpp(预计 SNR 下降 1-2dB) |

| 2 | ADC_CH1_CM_TOL=[10] | 具有共模变化容差的交流耦合/直流耦合输入,支持轨到轨(电源至地)(预计 SNR 下降约 35dB,仅在这种情况下支持高 CMRR) |

| 3 | ADC_CH1_CM_TOL=[11] | 保留 |

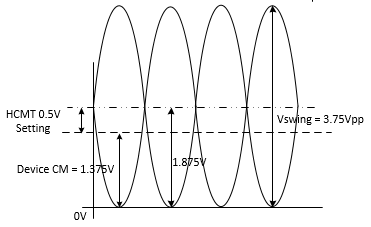

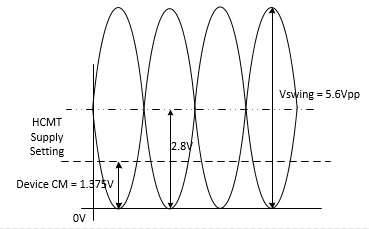

请注意,务必牢记器件在所有模式下的满标量程 (Vswing)。这对于较大的共模信号尤其重要,因为它们会限制有效的输入范围。例如,在模式 1 直流耦合中,器件内部共模电压 1.375V 的 500mVp 共模电压变体会将 Vswing 限制为 3.75Vpp 单端或 7.5Vpp (2.65Vrms) 差分。在模式 2 下,它可以支持 0V 至电源电压的共模范围,但在这两个极值处,都没有剩余空间可将差分信号应用于输入引脚。

图 1-2 模式 1 共模示例

图 1-2 模式 1 共模示例 图 1-3 模式 2 共模示例

图 1-3 模式 2 共模示例