ZHCADM8A October 2023 – May 2024 TAA5212 , TAA5242 , TAC5111 , TAC5112 , TAC5142 , TAC5211 , TAC5212 , TAC5242

2.1 差分交流耦合配置

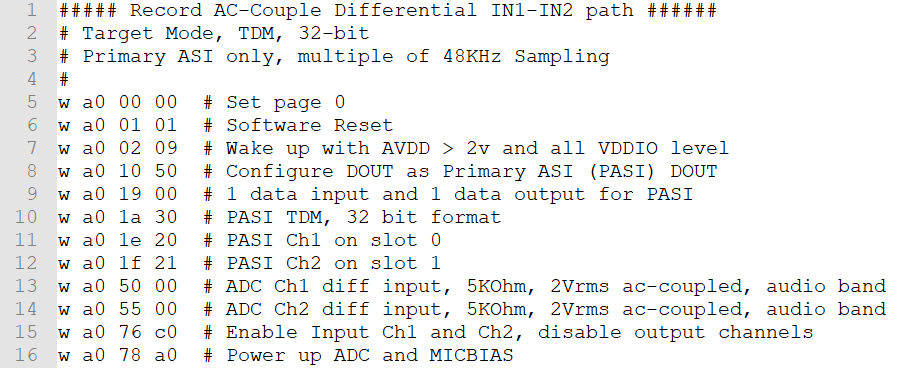

在交流耦合差分输入配置中,使用以下器件寄存器设置,并为 IN1P/M 提供相应的输入波形以实现满量程摆幅。针对不同的输入阻抗和共模容差设置 B0_P0_R80 (0x50) 和 B0_P0_R85 (0x55),更改第 13 行和 14 行中的寄存器设置。以下各图基于输入阻抗为 5kΩ 的模式 0。

图 2-1 差分交流耦合寄存器设置

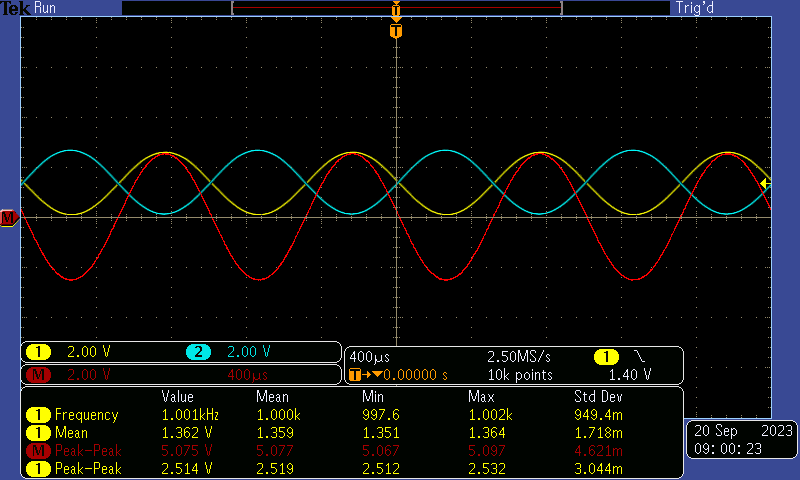

图 2-1 差分交流耦合寄存器设置 图 2-2 -1dBrG (0dBrG = 2Vrms) 时的差分交流耦合输入摆幅

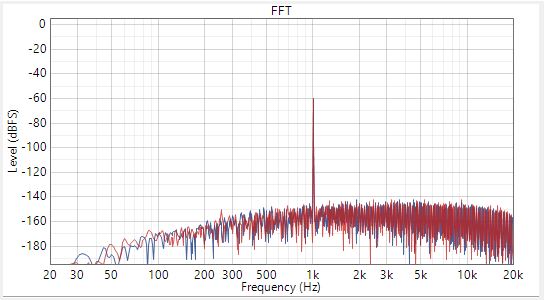

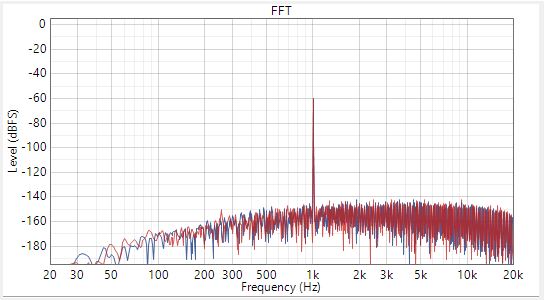

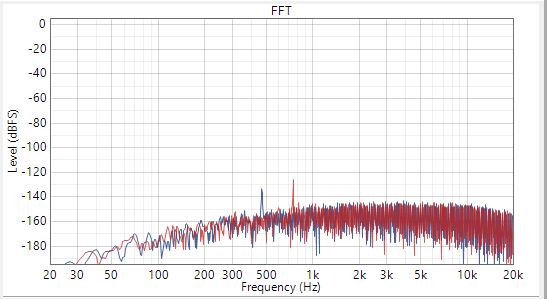

图 2-2 -1dBrG (0dBrG = 2Vrms) 时的差分交流耦合输入摆幅此处提供了 100mVpp 共模设置下的频率图,描绘了 -60dBrG 输入时的动态范围和输入交流信号短接至地时的 SNR。对于 2 种不同的共模容差,可以得到类似的图。 图 2-3 -60dBrG 输入时的差分交流耦合动态范围

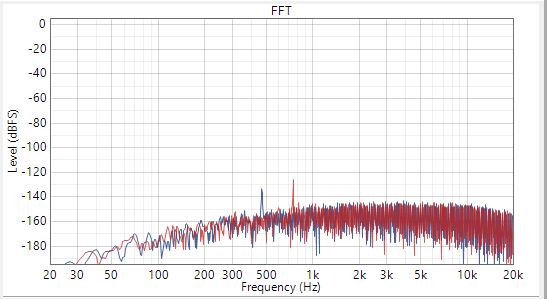

图 2-3 -60dBrG 输入时的差分交流耦合动态范围 图 2-4 输入交流信号短接至地时的 SNR

图 2-4 输入交流信号短接至地时的 SNR

图 2-3 -60dBrG 输入时的差分交流耦合动态范围

图 2-3 -60dBrG 输入时的差分交流耦合动态范围 图 2-4 输入交流信号短接至地时的 SNR

图 2-4 输入交流信号短接至地时的 SNR表 2-2 总结了三种不同通用容差根据不同软件控制器件型号的输入阻抗表现出的性能。表 2-3 总结了仅在差分交流耦合中支持 5KΩ 输入阻抗的硬件引脚控制器件的性能。

表 2-2 交流耦合性能总结 - 软件控制器件

| DR (dB) | SNR (dB) | THDN(-1dBrG 时) | ||||||||

|---|---|---|---|---|---|---|---|---|---|---|

| HCMT 模式 | Zin | TAC521x | TAC511x | TAA521x | TAC521x | TAC511x | TAA521x | TAC521x | TAC511x | TAA521x |

| 0 | 5K | 118 | 103 | 118 | 118 | 103 | 118 | -95 | -91 | -95 |

| 10K | 113 | 103 | 113 | 113 | 103 | 113 | -102 | -91 | -102 | |

| 40K | 101 | 103 | 102 | 102 | 103 | 102 | -97 | -91 | -97 | |

| 1 | 5K | 116 | 102 | 116 | 116 | 102 | 116 | -95 | -91 | -95 |

| 10K | 112 | 102 | 112 | 112 | 102 | 112 | -102 | -91 | -102 | |

| 40K | 100 | 102 | 101 | 101 | 102 | 101 | -96 | -91 | -97 | |

| 2 | 5K | 113 | 101 | 113 | 113 | 101 | 113 | -95 | -91 | -95 |

| 10K | 109 | 101 | 109 | 109 | 101 | 109 | -101 | 91 | -101 | |

| 40K | 99 | 101 | 100 | 100 | 101 | 100 | -96 | -91 | -96 | |

表 2-3 交流耦合性能总结 - 硬件控制器件

| DR (dB) | SNR (dB) | THDN(-1dBrG 时) | ||||||||

|---|---|---|---|---|---|---|---|---|---|---|

| MD5-MD4 | Zin | TAC5242 | TAC5142 | TAA5242 | TAC5242 | TAC5142 | TAA5242 | TAC5242 | TAC5142 | TAA5242 |

| 00 | 5K | 117 | 101 | 117 | 117 | 101 | 117 | -95 | -91 | -95 |