ZHCADO3 January 2024 DP83TC812R-Q1 , DP83TC812S-Q1

4.3.3 探测 CLKOUT 引脚

参考时钟频率和稳定性对于维持 PHY 的正常运行至关重要。不符合数据表中的规格可能会导致位错误、读取/写入问题或 PHY 完全无法运行。

请勿直接探测晶体,因为这会改变电路的容性负载并改变行为。相反,探测 CLKOUT 引脚(引脚 16),它是输入参考时钟的缓冲版本。

将频率保持在预期值的 ±100ppm 范围内:针对 RMII 从模式为 (40.995Mhz - 50.005Mhz),而针对所有其他模式为 (24.9975Mhz - 25.0025Mhz)。

表 4-2 25MHz 晶体要求

|

25MHz 晶体要求 |

||

|---|---|---|

|

频率 |

25 |

MHz |

|

最大频率容差及稳定性与温度及老化之间的关系 |

±100 |

ppm |

|

最大等效串联电阻 |

100 |

Ω |

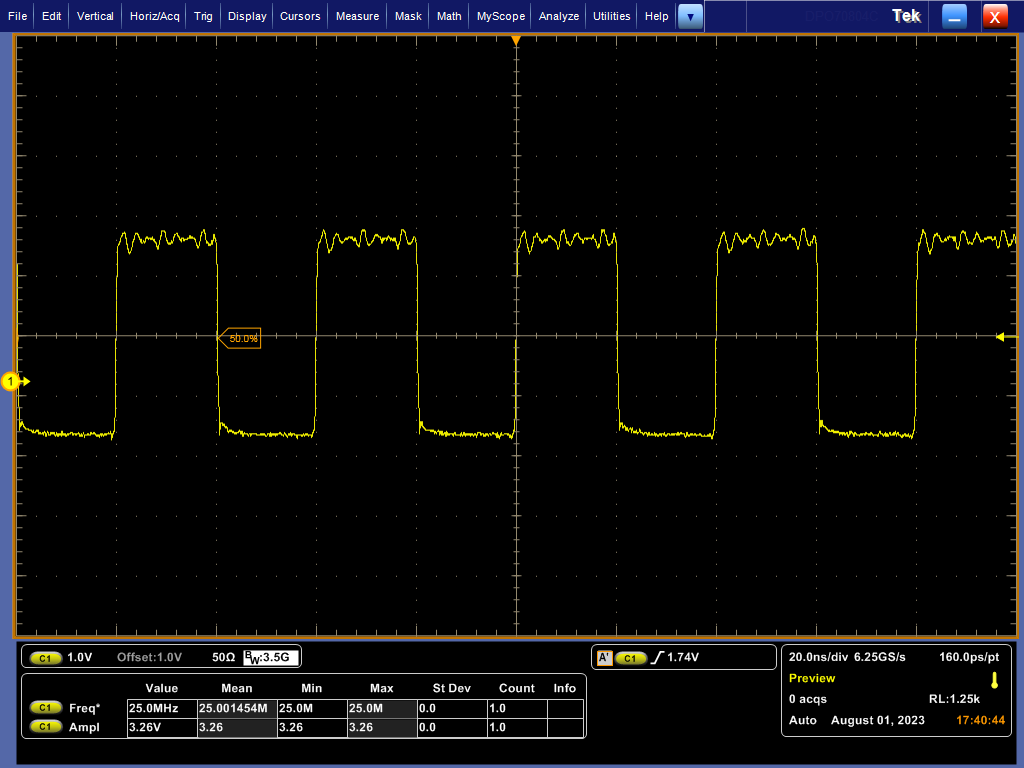

图 4-1 DP83TC812 CLK_OUT 测量

图 4-1 DP83TC812 CLK_OUT 测量注: 确认振幅等于 VDDMAC 且频率处于 ±100ppm (24.9975Mhz - 25.0025Mhz) 范围内