ZHCADO3 January 2024 DP83TC812R-Q1 , DP83TC812S-Q1

4.11 调试 MAC 接口

MAC 接口通信故障的常见原因是未正确设置所需的 MAC 接口模式。例如,如果启用了 SGMII 模式但 PCB 旨在用于 RGMII 通信,则链路可以接通,但 ping 命令会失败。请参阅 DP83TC812 原理图检查清单的 Strap 配置工具,以确认选择了正确的 MAC 接口模式。也可以通过写入寄存器 0x600[3]、0x608[9]、0x648[6] 来选择 MAC 模式。

简化千兆位媒体独立接口(RGMII)

用于 RGMII 协议的信号如下所示:

图 4-9 RGMII 信令

图 4-9 RGMII 信令RGMII 协议具有一定的时序限制,必须满足这些限制才能正确接收数据。下面的表 4-9 中显示了这些时序限制。即,必须在接收器的输入端保持至少 1ns 的建立时间和 1ns 的保持时间。为了满足此要求,必须在时钟和数据信号之间引入一定量的偏斜。这种偏斜可能由 MAC 或 PHY 引入,也可能作为 PCB 布线长度的一部分。DP83TC812 具有两种模式:对齐模式和移位模式,适用于 RX 和 TX 信号。这些模式可通过自动加载 (bootstrap) 选择,或在寄存器 0x602 中进行调整。注意,如果在 PHY TX 信号上启用移位模式,则 MAC 发送数据时不会出现偏斜。同样,如果在 PHY RX 信号上选择对齐模式,则必须将 MAC 设置为 RX 移位模式。表 4-8 显示了正确的 MAC 和 PHY RGMII 延迟配置。

MAC 配置 | 所需的 PHY 配置 |

|---|---|

| Rx 侧的 RGMII 对齐 | Rx 侧的 RGMII 移位 |

| Rx 侧的 RGMII 移位 | Rx 侧的 RGMII 对齐 |

| Tx 侧的 RGMII 对齐 | Tx 侧的 RGMII 移位 |

| Tx 侧的 RGMII 移位 | Tx 侧的 RGMII 对齐 |

在 RGMII RX 移位模式下,PHY 将 RX_CLK 移至 RX_Data 信号之前大约 3ns。

当使用 PHY 的 TX 移位模式时,PHY 希望 TX_CLK 和 TX_Data 信号在其引脚处对齐,并且数据在内部移位。

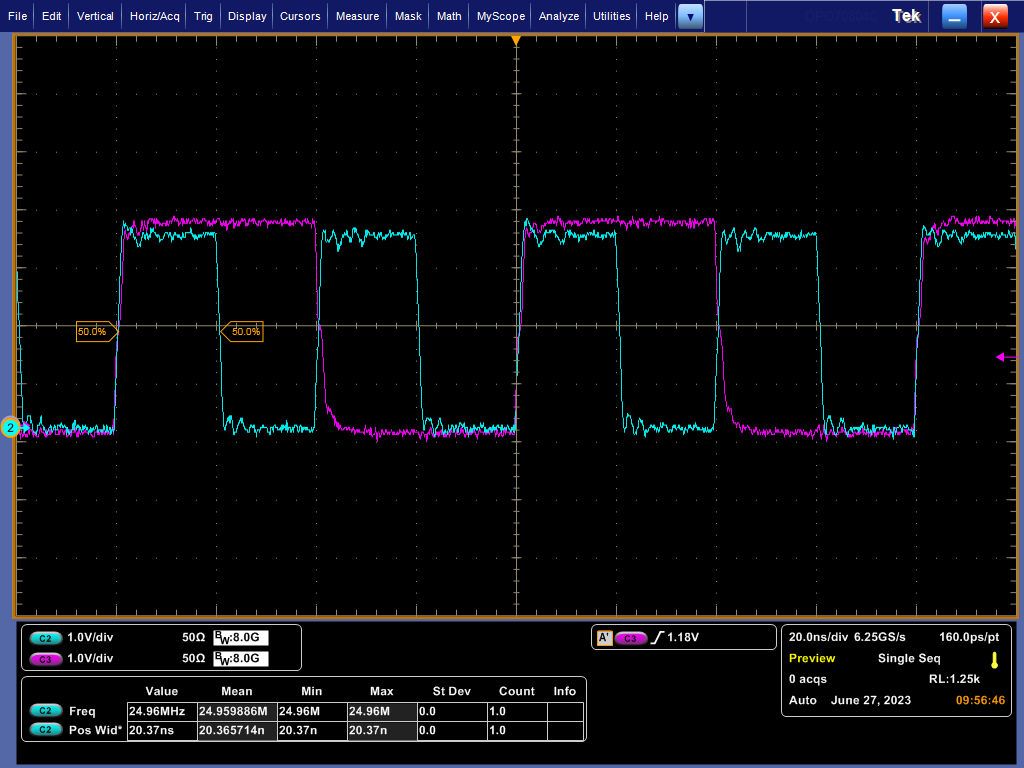

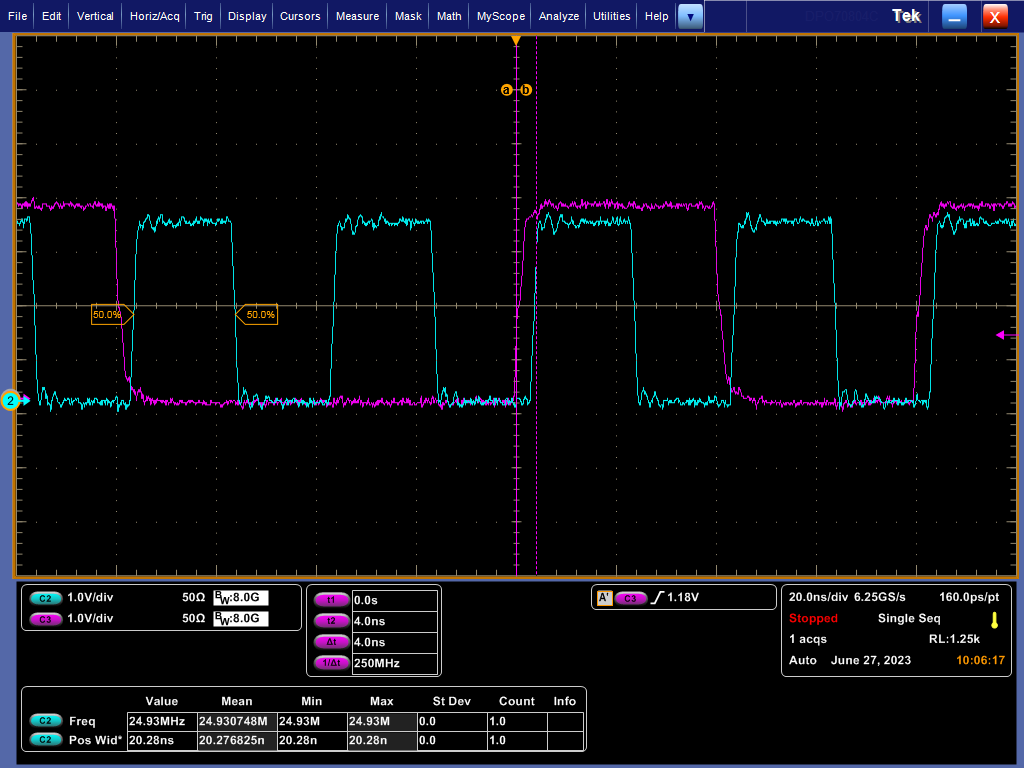

下面的参考波形显示了启用移位或对齐模式对 RX_D0 信号的影响。

图 4-10 RGMII 对齐模式下的 RX_CLK 和 RX_D0 时序

图 4-10 RGMII 对齐模式下的 RX_CLK 和 RX_D0 时序 图 4-11 RGMII RX 移位模式下的 RX_CLK 和 RX_D0 时序

图 4-11 RGMII RX 移位模式下的 RX_CLK 和 RX_D0 时序| 参数 | 测试条件 | 最小值 | 典型值 | 最大值 | 单位 |

|---|---|---|---|---|---|

| Tcyc | TX_CLK/时钟周期时长 | 36 | 40 | 44 | ns |

| Tsetup(align) | TX_D[3:0],TX_CTRL 设置至 TX_CLK(对齐模式) | 1 | 2 | ns | |

Thold(align) | TX_D[3:0],TX_CTRL 保持至 TX_CLK(对齐模式) | 1 | 2 | ns |

| 参数 | 测试条件 | 最小值 | 典型值 | 最大值 | 单位 |

|---|---|---|---|---|---|

| Tskew(align) | RX_D[3:0],RX_CLK 后的 RX_CTRL 延迟(对齐模式) | -750 | 750 | ps | |

| Tskew(shift) | RX_D[3:0],RX_CLK 后的 RX_CTRL 延迟(已启用移位模式,默认设置) | 2 | ns | ||

Tcyc | RX_CLK/时钟周期时长 | 36 | 40 | 44 | ns |

Duty_G | RX_CLK/占空比 | 45 | 50 | 55 | % |

Tr/Tf | RX_CLK/上升、下降时间(20% 至 80%,Cload=5pF) | 1.2 | ns |

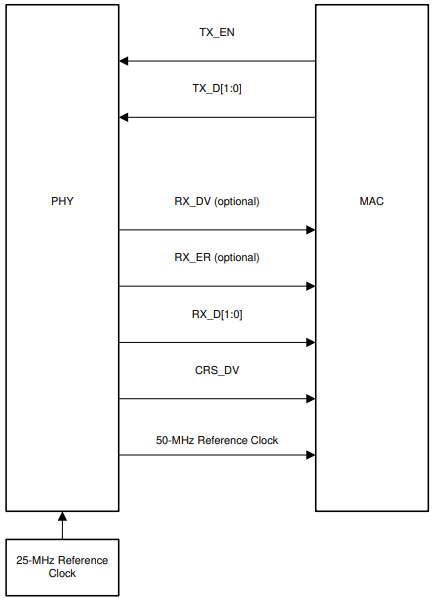

简化媒体独立接口 (RMII)

使用 RMII 模式时,存在两个独立的配置:RMII 主模式和 RMII 从模式。在 RMII 主模式下,PHY 在其 XI 引脚上获得一个 25MHz 输入时钟,并在其 RX_D3 引脚(引脚 23)上输出一个 50MHz 时钟信号,以发送至 MAC。在 RMII 从模式下,PHY 在 XI 引脚上接收来自 MAC 或外部振荡器的 50MHz 时钟信号。必须通过自动加载 (bootstrap) 选择正确的 RMII 模式(这不能通过寄存器写入来更改),以便 PHY 需要正确的参考时钟(25Mhz 或 50Mhz)。请参阅 DP83TC812 原理图检查清单 strap 配置工具,确保选择正确的 RMII 模式。接下来,探测 PHY 的 CLKOUT 引脚,如果使用 RMII 主模式,则确保出现 25MHz 信号,如果使用 RMII 从模式,则出现 50MHz 信号。

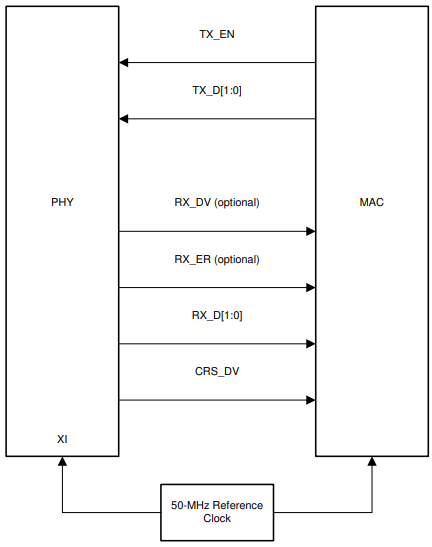

用于 RMII 协议的信号如下所示。

图 4-12 RMII 主信令

图 4-12 RMII 主信令 图 4-13 RMII 从信令

图 4-13 RMII 从信令