ZHCADR6 November 2021 TLV3601 , TLV3601-Q1 , TLV3603 , TLV3603-Q1

瞬态仿真结果

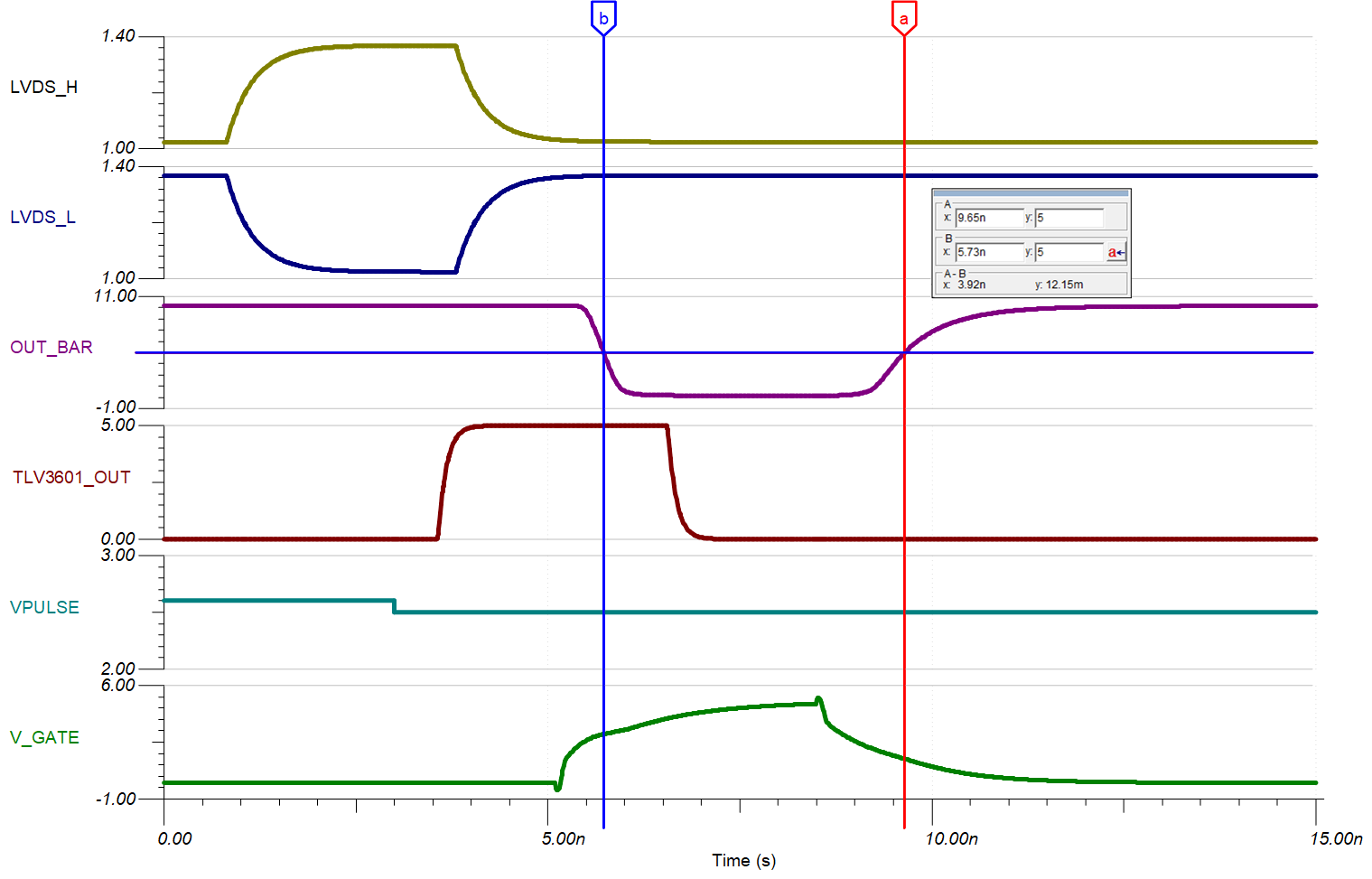

使用馈入 TLV3604 的“VPULSE”脉冲波形发生器,低于 1Ω 负载电阻的电压被监控为 OUT_BAR。当 GaN FET 的栅极被充分驱动时,漏极处的明显电压约为 0V。下图展示了初始仿真结果。

初始仿真结果

初始仿真结果如初始仿真结果所示,脉冲宽度比设计要求 (3.92ns) 宽约 0.6ns。部分原因是 EPC2019 栅极上的串联电阻用于避免感应振铃导致的电压过应力。为了缩短 GaN FET 驱动器和 GaN FET 的关断时间,可将 LMG1020 的 OUTL 输出短接到 EPC2019 的栅极,如 LMG1020 适用于 1ns 脉冲宽度应用的 5V、7A/5A 低侧 GaN 和 MOSFET 驱动器 数据表典型应用 一节所建议。

修改了原理图以改善脉冲宽度

修改了原理图以改善脉冲宽度接下来,再次对电路进行仿真,看看减小后的脉冲宽度是否符合设计要求。

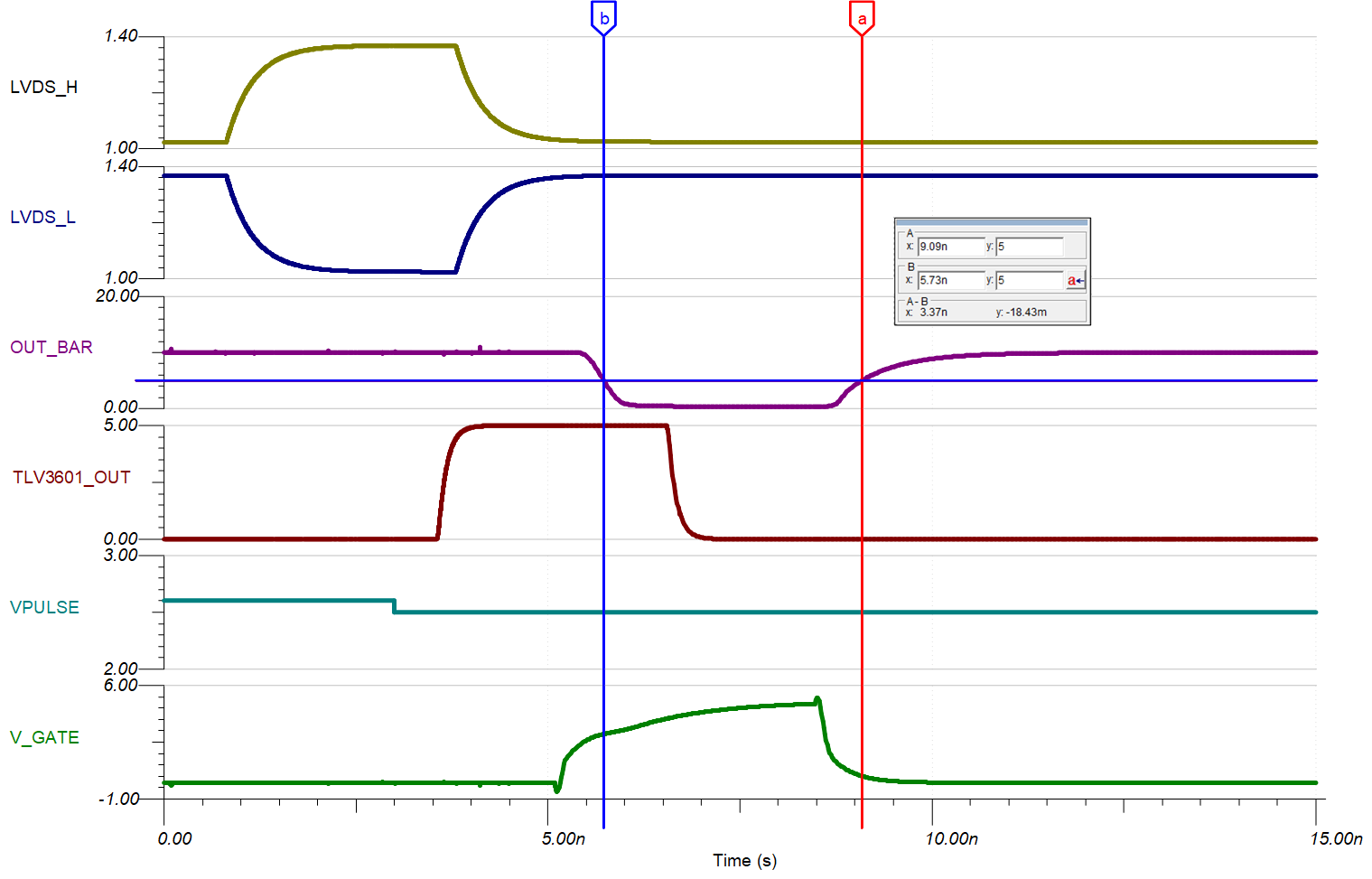

移除电阻器后的仿真结果

移除电阻器后的仿真结果如移除电阻器后的仿真结果中的仿真结果所示,OUT_BAR 的宽度略超出设计要求,脉冲宽度为 3.37ns。为了进一步改善脉冲宽度,将更窄的 LVDS 脉冲发送到 TLV3601。为此,驱动 TLV3604 非反相输入的发生器脉冲宽度 VPULSE 会减小。发生器脉冲宽度调整为 2.5ns,以确保脉冲宽度符合设计要求。符合设计标准的仿真展示了符合设计要求的 2.70ns 仿真脉冲宽度。

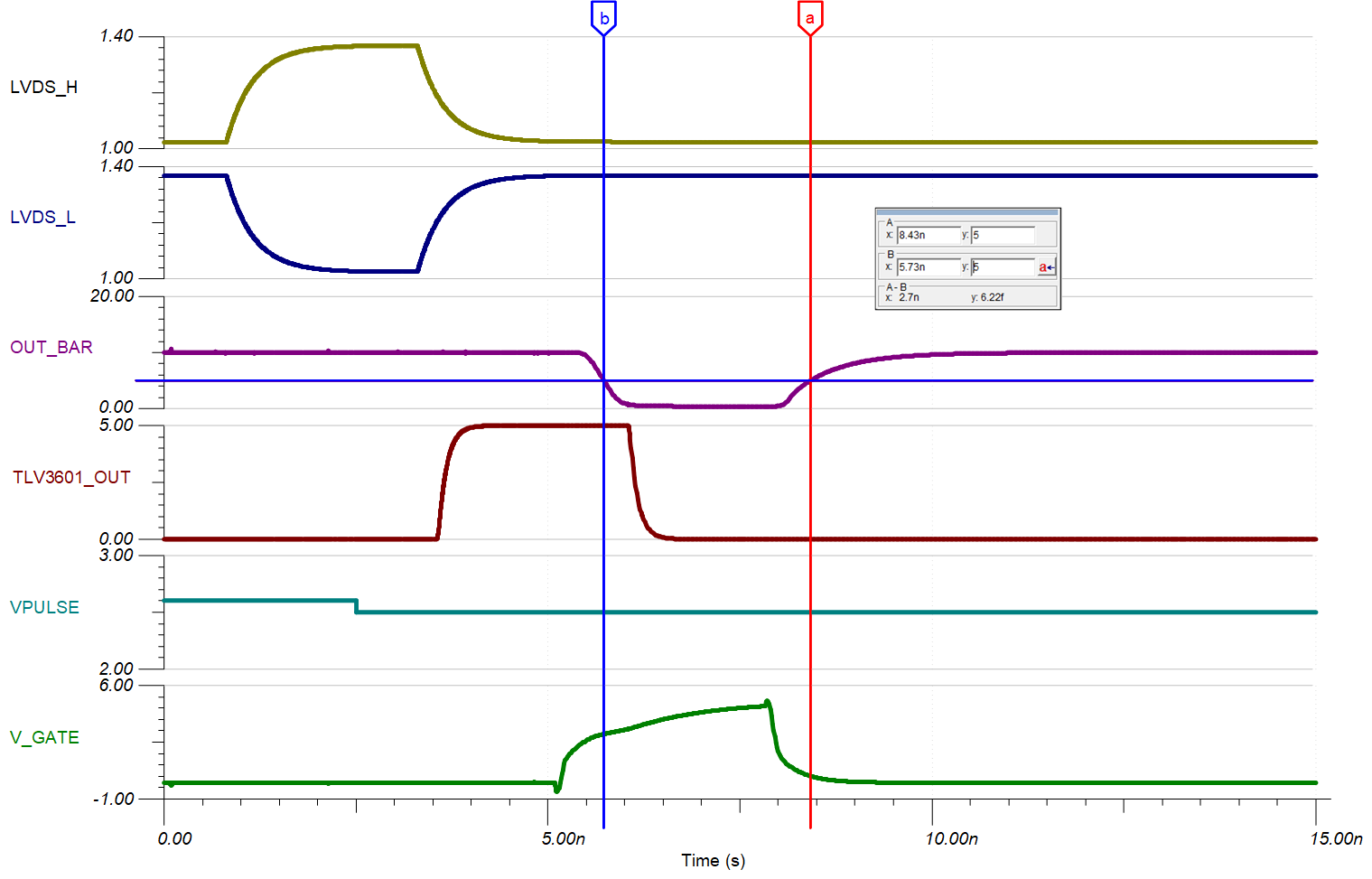

符合设计标准的仿真

符合设计标准的仿真