ZHCADT8A December 2023 – June 2024 TAA5212 , TAC5111 , TAC5112 , TAC5211 , TAC5212 , TAD5112 , TAD5212

3.1 ADC 采样速率转换

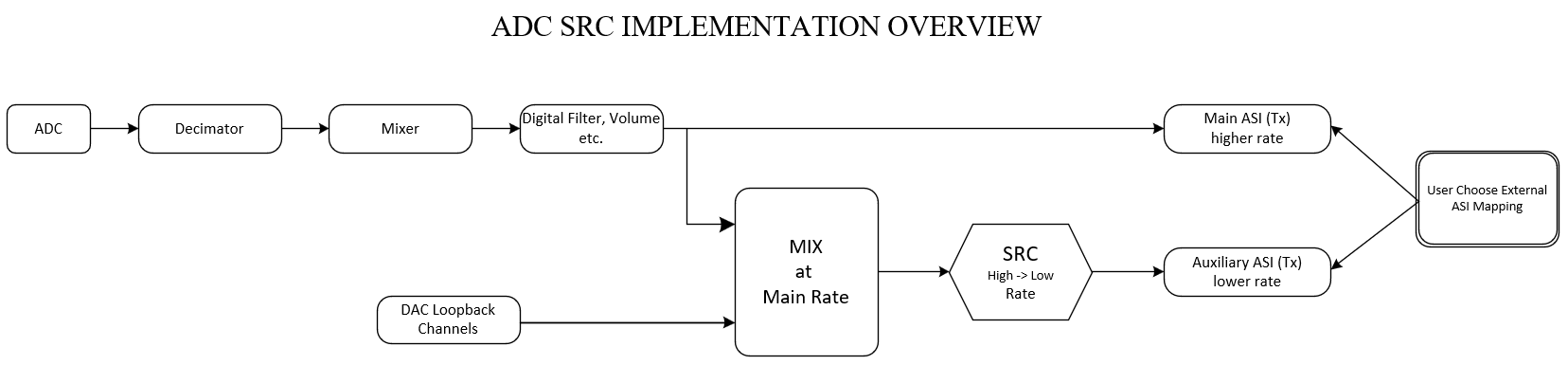

以下方框图显示了默认模式下的 ADC SRC 流程概述,其中以较高采样速率(主 Fs)运行的 ADC 输入转换为较低采样速率(辅助 Fs),并且在另一个 ASI 上可用。用户可以选择使用主要 ASI 或次要 ASI 以及较高速率或较低速率的接口。当从较低速率选择主 Fs 时,该流程同样适用,因此 SRC 将从较低速率转换为较高速率。

SRC 流程可以选择与 DAC 环回数据进行混频,例如将来自主机的音频数据添加到录制的语音数据。

图 3-1 TAx5x1x ADC SRC 概述 - 默认模式

图 3-1 TAx5x1x ADC SRC 概述 - 默认模式用户可以在混频时观察电平,并设置系数,以确保输出不超过允许的最大值,因为较高的电平会导致削波或失真。下列公式给出了混频器输出电平:

对于 ADC 混频器,设置混频系数的公式如下所示,其中 w 表示幅度的权重或比例。例如,w=0.5 表示幅度的一半,在 32 位 DAC 混频器系数中则转换为 'h40000000。一些路径系数默认为 'h7FFFFFFF,其满量程幅度为 1。ADC 混频器系数通过寄存器页面地址 0x0A 和寄存器地址 0x08 至 0x47 进行配置。

对于数字环回(ADC 至 DAC)混频器,设置混频系数的公式与上述 ADC 混频器公式相同,并通过寄存器页面地址 0x0A 以及寄存器地址 0x48 至 0x67 进行设置。

对于 ADC 辅助混频器,设置混频系数的公式如下所示,其中 w 表示幅度的权重或比例。该辅助 ADC 混频器系数通过寄存器页面地址 0x0B 和寄存器地址 0x30 至 0x37 进行配置。

后续各节将介绍此 ADC SRC 的一些示例。