ZHCADZ6A April 2024 – August 2024 AM62P , AM62P-Q1

3.1.1 LMBench

LMBench 是一套适用于处理器内核和操作系统基元的微基准测试工具。存储器带宽和延迟相关测试非常适用于现代嵌入式处理器。每次运行的结果略有不同 (<10%)。

LMBench 基准测试 bw_mem 测量实现的存储器复制性能。通过使用参数 cp,基准测试执行数组复制,bcopy 参数使用运行时 glibc 版本的 memcpy() 标准函数。利用 SIMD 等实现更高性能,在实施高度优化的基础上进行 glibc 实践。等于或小于给定级别高速缓存大小的 size 参数可测量进行典型的 for 循环或 memcpy() type 操作的软件可实现的存储器带宽。通常用于计算外部存储器带宽。带宽根据字节读写(每读写 1 字节计为 1)计算,结果约为 STREAM 复制结果的一半。此基准测试还允许利用 -P 参数创建并行线程。为了获得较大多核存储器带宽,需要创建的线程数量应等同于操作系统可用的内核数量,即 4 个 (AM62Px Linux (-P 4))。为了显示 AM62Px 的完整性能特征,LMBench 测试是在内核数量和时钟频率的完整阶乘组合上实施的。下面的代码块展示了执行 LMBench 命令的终端打印输出。

root@am62pxx-evm:~# bw_mem 8M bcopy

8.00 1956.71

root@am62pxx-evm:~# bw_mem -P 2 8M bcopy

8.00 3122.66

root@am62pxx-evm:~# bw_mem -P 4 8M bcopy

8.00 3605.80

root@am62pxx-evm:~# bw_mem 8M cp

8.00 1012.27

root@am62pxx-evm:~# bw_mem -P 2 8M cp

8.00 1568.78

root@am62pxx-evm:~# bw_mem -P 4 8M cp

8.00 1874.32

表 3-1 展示了相对于理论线速测得的带宽和效率。使用的线速计算方式为:LPDDR4 MT/s 速率 x 宽度 ÷ 2(构成复制的读取和写入均会消耗总线)。

| 命令 | 说明 | Arm-Cortex-A53 (1.25GHz),LPDDR4(3200MT/s、32 位)[MB/s] | LPDDR4 效率 [%] | Arm-Cortex-A53 (1.4GHz),LPDDR4(3200MT/s、32 位)[MB/s] | LPDDR4 效率 [%] |

|---|---|---|---|---|---|

| Bw_mem 8M bcopy | 单核,glibc memcpy | 1,911 | 30 | 1,956 | 31 |

| bw_mem -P 2 8M bcopy | 双核,glibc memcpy | 3,052 | 48 | 3,122 | 49 |

| bw_mem -P 4 8M bcopy |

四核,glibc memcpy | 3,571 | 56 | 3,605 | 56 |

| Bw_mem 8M cp | 单核,内联复制循环 | 1,003 | 16 | 1,012 | 16 |

| bw_mem -P 2 8M cp |

双核,内联复制循环 | 1,562 | 24 | 1,568 | 25 |

| bw_mem -P 4 8M cp |

单核,内联复制循环 | 1,862 | 29 | 1,874 | 29 |

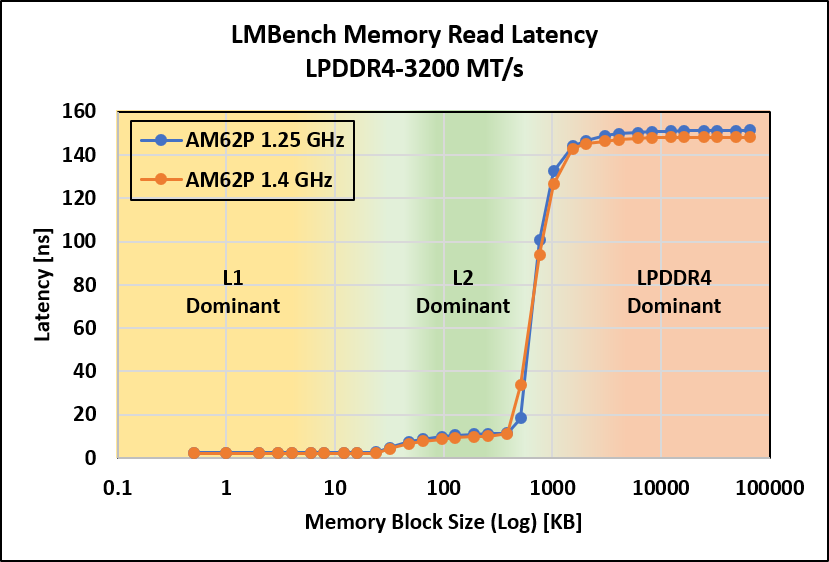

LMBench 基准测试 lat_mem_rd 用于测量外部存储器 (AM62Px LPDDR4) 观察到的存储器存取延迟和高速缓存命中率。有两个参数,分别是事务大小(64,如以下代码块所示)和读取跨度 (512)。选择这两个数值来测量高速缓存和外部存储器的延迟,而不是处理器数据预取器或其他推测性执行的延迟。存取模式可实现预取,但此基准测试特别适用于无法实现预取的存取模式下的相关测量。

下面的代码块展示了执行 lat_mem_rd 命令的终端打印输出。左列是数据存取模式的大小(单位为兆字节),右侧是往返读取延迟(单位为纳秒)。此命令在 1.25GHz 和 1.4GHz 的 Arm-Cortex-A53 时钟频率下执行。

root@am62pxx-evm:~# lat_mem_rd 64 512

"stride=512

0.00049 2.145

0.00098 2.145

0.00195 2.145

0.00293 2.145

0.00391 2.145

0.00586 2.145

0.00781 2.145

0.01172 2.145

0.01562 2.145

0.02344 2.289

0.03125 4.179

0.04688 6.494

0.06250 7.748

0.09375 8.626

0.12500 9.283

0.18750 9.764

0.25000 9.976

0.37500 11.156

0.50000 33.705

0.75000 94.007

1.00000 126.437

1.50000 142.957

2.00000 145.089

3.00000 146.336

4.00000 147.029

6.00000 147.626

8.00000 147.867

12.00000 148.112

16.00000 148.169

24.00000 148.243

32.00000 148.219

48.00000 148.284

64.00000 148.291图 3-1 展示了 1.25GHz 和 1.4GHz 下存储器延迟结果的连接散点图。基于存储器块大小(x 轴),该图可分为三个区域。第一个区域是被存取的存储器块小于 L1 高速缓存时。假定数据完全位于 L1 内部,因此该区域中的这种延迟是 L1 高速缓存延迟的近似估计值。第二个区域是被访问的存储器块大于 L1 但小于 L2 高速缓存时。该区域中的延迟是 L1、L2 和 LPDDR4 延迟的混合。可以假设该区域中间的延迟是 L2 延迟的近似表示。第三个区域是访问的存储器块大于 L2 高速缓存时。该区域中的最后一个读数反映了 LPDDR4 延迟。

图 3-1 存储器读取延迟

图 3-1 存储器读取延迟表 3-2 展示了 Arm-Cortex-A53 读取延迟的摘要。

| 存储器 | Arm-Cortex-A53 (1.25GHz) [ns] | Arm-Cortex-A53 (1.4GHz) [ns] |

|---|---|---|

| L1 高速缓存 | 2.4 | 2.1 |

| L2 高速缓存 | 10.4 | 9.2 |

| LPDDR4-3200MT/s | 151.3 | 148.2 |