ZHCAE26 May 2024 BQ769142 , BQ76942 , BQ76952 , BQ76972

- 1

- 摘要

- 1 常规操作常见问题解答

-

2 控制 FET 常见问题解答

- 2.1 高侧与低侧栅极驱动之间有哪些权衡?

- 2.2 BQ769x2 是否可用于低侧 FET 驱动?

- 2.3 低侧开关是否需要 CP1 电容器?

- 2.4 BQ769x2 在上电时需要多长时间才能使 FET 导通?

- 2.5 充电 (CHG) 和放电 (DSG) 引脚的典型电压是多少?

- 2.6 预充电 (PCHG) 和预放电 (PDSG) 引脚的电压范围是多少?

- 2.7 如何实现更快的 DSG 栅极关断?

- 2.8 为什么在 CONFIG_UPDATE 模式下配置数据存储器寄存器时 FET 会关断?

- 2.9 是否有方法手动控制 PCHG 和 PDSG?

- 2.10 可以将 NFET 与 PDSG 引脚配合使用吗?

- 2.11 禁用时,PDSG 和 PCHG 处于什么状态?

- 2.12 如何禁用放电 FET (DFET) 和充电 FET (CFET)?

- 2.13 BQ769x2 可以在 SLEEP 模式下保持 PDSG 导通吗?

- 3 库仑计数器 (CC) 和 ADC 常见问题解答

- 4 通信协议和编程常见问题解答

- 5 校准和温度检测常见问题解答

- 6 电芯均衡常见问题解答

-

7 器件电源和状态开关常见问题解答

- 7.1 该器件支持的电池包的最大电压是多少?

- 7.2 使用电荷泵时允许的最大电池包电压是多少?

- 7.3 是否有必要将 BAT- 连接到 VSS?

- 7.4 其他信号 GND 需要如何连接到 PACK- 吗?

- 7.5 是否需要在 VC0 和 VC1 之间放置一个电容器?

- 7.6 对于我的原理图设计,推荐的典型无源器件值是多少?

- 7.7 两个可编程 LDO 能够提供多大的电流?

- 7.8 可以将 LDO 输入晶体管连接到电池包中比 BAT+ 电压低的电芯来提高效率吗?

- 7.9 在参考设计中,为什么要在 VC16 和 PACK+ 之间以及 PACK+ 和 PACK- 之间放置两个电容器?

- 7.10 BQ769x2 器件系列有哪些不同的低功耗模式?

- 7.11 MCU 如何知道 BQ769x2 处于关断状态?

- 7.12 是否可以禁用 SHUTDOWN 模式?

- 7.13 BQ769x2 如何退出 SHUTDOWN 模式?

- 7.14 什么是软关断?如何退出软关断模式?

- 8 评估模块和 BQStudio 常见问题解答

- 9 其他指导材料

- 10参考资料

2.7 如何实现更快的 DSG 栅极关断?

有两种通用方法可以缩短栅极关断时间。

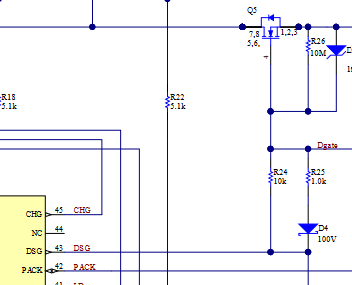

第一种方法如图 2-1 所示,通过使用二极管 (D4) 为 FET 的栅极提供一条电阻比导通路径更低的路径来释放存储的电荷,从而提供了一种加速关断过程的低成本设计。通过改变电阻,可以根据需要增加或减少关断时间。

图 2-1 采用单个二极管 (D4) 的第一种加速配置

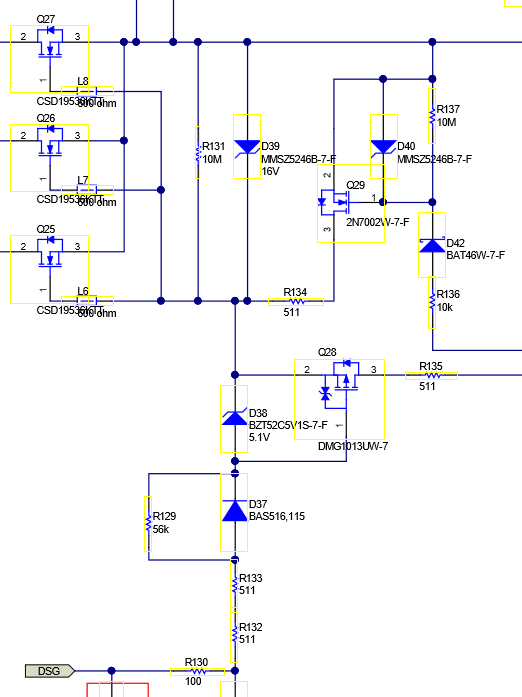

图 2-1 采用单个二极管 (D4) 的第一种加速配置第二种方法如图 2-2 所示。此电路可以更快地将 PMOS 驱动为低电平,从而为 FET 的电荷提供了从栅极流向 PACK+ 的替代路径。虽然这种配置更昂贵,但在多个 FET 并联的情况下,由于能够获得更低的电阻,因此它是一个很好的选择。如果用户仅使用一个或两个 FET,第一种方法更具成本效益。

图 2-2 采用 PMOS 和二极管(D37 和 Q28)的第二种多 FET 应用配置

图 2-2 采用 PMOS 和二极管(D37 和 Q28)的第二种多 FET 应用配置