ZHCAE33 December 2022 AMC1202 , AMC1302 , AMC1306M05 , AMC22C11 , AMC22C12 , AMC23C10 , AMC23C11 , AMC23C12 , AMC23C14 , AMC23C15 , AMC3302 , AMC3306M05

3.3 G 点 - 直流/直流级谐振回路电流检测

本节详细介绍了开关谐振回路(G 点)的电流检测要求。在谐振 CLLLC 双向隔离式直流/直流转换器中,同步整流需要进行过零检测 (ZCD),这有助于降低导通损耗并提高系统效率。

图 3-6 在隔离式直流/直流转换器的初级或次级谐振回路处进行电流检测

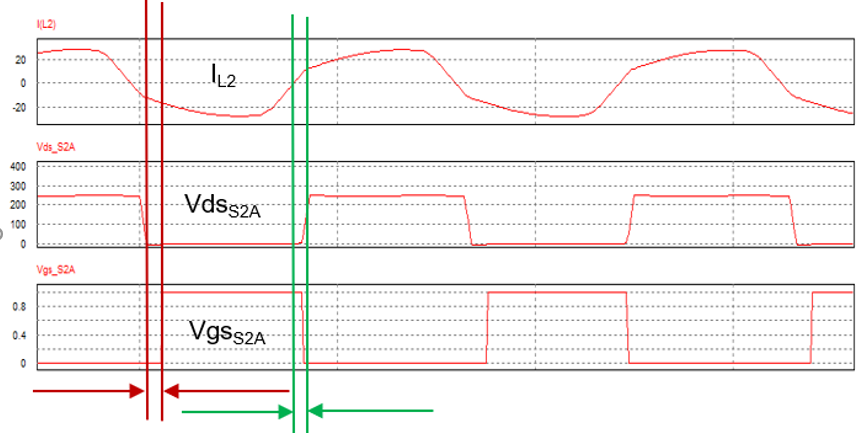

图 3-6 在隔离式直流/直流转换器的初级或次级谐振回路处进行电流检测在图 3-6 中,两条绿色光标线表示过零和次级侧 FET 导通之间的传播延迟。

图 3-7 过零检测的传播延迟

图 3-7 过零检测的传播延迟在 CLLLC 拓扑中,ZCD 电路的先进实现方式是将电流互感器 (CT) 或 Rogowski 线圈与谐振电容器串联在一起放置在初级侧和次级侧。CT 或 Rogowski 线圈方法的典型传播延迟在 100ns 到 200ns 之间。该延迟可能在 CLLLC 拓扑中导致显著损耗,从而对直流/直流转换器的整体效率产生负面影响。假设峰值电流约为 30A、谐振开关频率为 500kHz 且导通延迟为 100ns,则体二极管 FET(正向电压为 4.5V)承载着 9.3A 的电流,直到 FET 导通为止。这导致每个 FET 的峰值能量损耗约为 42W。

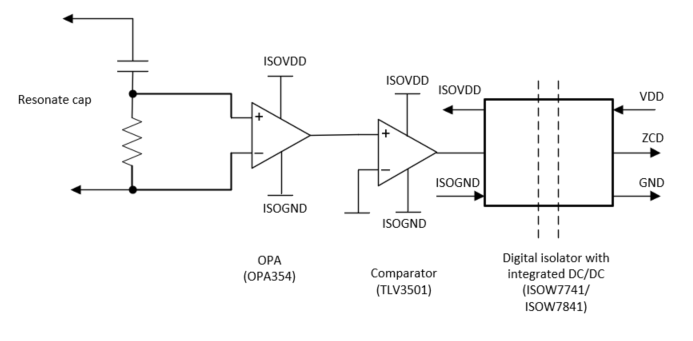

图 3-8 展示了一种替代方法。在该方法中,谐振电容器的电压与微分器电路相结合,以重新生成正弦电流。重新生成的正弦信号由差分到单端 OPA (OPA354) 和快速比较器 (TLV3501) 进一步处理来进行过零检测。

图 3-8 采用 ISOW7741、ISOW7841 的 ZCD 电路

图 3-8 采用 ISOW7741、ISOW7841 的 ZCD 电路过零信号由数字隔离器(ISOW7741 或 ISOW7841)进行隔离。这些数字隔离器集成了隔离式直流/直流转换器,可为 OPA 和比较器器件生成隔离式电源。OPA354、TLV3501 和 ISOW7741 的传播延迟分别为 0.6ns、4.5ns 和 10.7ns,因此整个设计的总传播延迟为 15.8ns,约为 CT 或 Rogowski 线圈方法的十分之一。假设开关频率和峰值电流与之前的示例相同,一个 FET 中的峰值能量损耗可从 42W 降至仅 6.7W(对整体效率产生积极影响)。