ZHCAE44A June 2024 – August 2024 TMS320F280021 , TMS320F280023 , TMS320F280023C , TMS320F280025 , TMS320F280025C , TMS320F280033 , TMS320F280034 , TMS320F280037 , TMS320F280037C , TMS320F280039 , TMS320F280039C , TMS320F280041 , TMS320F280041C , TMS320F280045 , TMS320F280049 , TMS320F280049C , TMS320F28075 , TMS320F28076 , TMS320F28374D , TMS320F28374S , TMS320F28375D , TMS320F28375S , TMS320F28376D , TMS320F28376S , TMS320F28377D , TMS320F28377S , TMS320F28378D , TMS320F28378S , TMS320F28379D , TMS320F28379S , TMS320F28P550SJ , TMS320F28P650DH , TMS320F28P650DK , TMS320F28P650SH , TMS320F28P650SK

3.3 CLB 配置

CLB 是 C2000 MCU 上的外设,包含若干查询表 (LUT)、有限状态机 (FSM) 和计数器,可配置用来执行复杂逻辑运算。LUT 子模块可用于实现简单的组合逻辑,例如使信号反相或对多个信号进行“与”操作。FSM 子模块可用于实现基于状态的逻辑,例如 SR 锁存器。计数器子模块包含一个 32 位计数寄存器,可用于执行一些运算,例如计算信号处于高电平的周期数以及对时钟信号进行分频。将这些子模块互连可以在各种应用中实现许多不同的功能。每个 CLB 逻辑块包含一个高级控制器 (HLC),可由 CLB 内的信号触发来执行预设的指令。这些指令包括添加寄存器、减去寄存器、在 CLB 中的寄存器之间移动数据、向 CPU 发送中断信号以及向 CPU 发送数据和从 CPU 接收数据。

在 HHC LLC 设计中,需要 2 个 CLB 逻辑块。对于同步整流 (SR) 控制,因为比较器事件决定了初级侧 PWM 的关断时序,所以挑战在于如何提前使用正常的 EPWM 配置来定义 SR PWM 的导通时间。因此,使用 CLB 来简化 HHC LLC 的 SR 控制。有关更多详细信息,请参阅利用 CLB 实现基于硬件的同步整流控制。

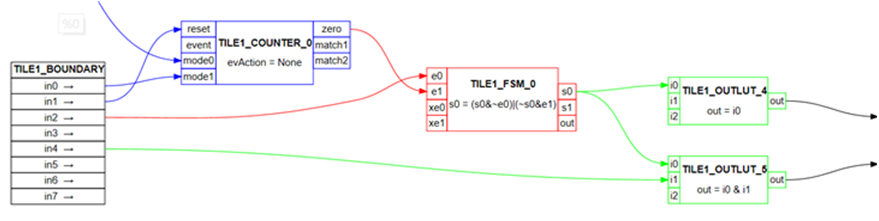

对于初级侧 PWM 配置,CLB 用于确保高侧和低侧 PWM 信号(EPWM1A 和 EPWM1B)的脉冲宽度相同。如图 3-3 所示,CLB 用于根据 EPWM1A 的 AQ 模块输出信号为 EPWM1B 生成 AQ 模块输出信号。EPWM1A 的 AQ 模块输出信号用于控制 CLB 计数器的计数器方向,该计数器可在 EPWM1A 清除低电平后开始递减计数。通常使用的方法是生成对称计数器信号。然后,通过利用 EPWM1A 的下降沿和计数器 = 0 事件,FSM 可生成 EPWM1B 的预期信号。

图 3-3 初级侧 PWM 的 CLB 逻辑

图 3-3 初级侧 PWM 的 CLB 逻辑如表 3-1 所示,可以通过使用 CLB 多路复用器输出使能寄存器 CLB_OUT_EN 将 FSM0_S0 直接分配到 CLB1 模块的输出 5,从而使用 FSM0_S0 来覆盖 EPWM1B 的 AQ 模块输出。

| CLB 输出 | CLB 输出 | CLB1Destination | CLB2Destination | CLB3Destination | CLB4Destination |

|---|---|---|---|---|---|

| 0 | OUTLUT0 | EPWM1A | EPWM2A | EPWM3A | EPWM4A |

| 1 | OUTLUT1 | EPWM1A_OE | EPWM2A_OE | EPWM3A_OE | EPWM4A_OE |

| 2 | OUTLUT2 | EPWM1B | EPWM2B | EPWM3B | EPWM4B |

| 3 | OUTLUT3 | EPWM1B_OE | EPWM2B_OE | EPWM3B_OE | EPWM4B_OE |

| 4 | OUTLUT4 | EPWM1A_AQ | EPWM2A_AQ | EPWM3A_AQ | EPWM4A_AQ |

| 5 | OUTLUT5 | EPWM1B_AQ | EPWM2B_AQ | EPWM3B_AQ | EPWM4B_AQ |

| 6 | OUTLUT6 | EPWM1A_DB | EPWM2A_DB | EPWM3A_DB | EPWM4A_DB |

| 7 | OUTLUT7 | EPWM1B_DB | EPWM2B_DB | EPWM3B_DB | EPWM4B_DB |

请注意,要将上升沿延迟添加到 EPWM1B 最终输出信号,首先使 CLB 生成的 FSM 输出反相,然后可以在 DB 模块内启用下降沿延迟。

此外,还需要在 EPWM1B 的下降沿为 EPWM1 模块生成同步事件,这可通过将 FSM_S0 输出路由到 CLB 输出(输出 4),然后通过 EPWM X-BAR 配置同步方案来实现。

图 3-4 展示了完成的 CLB 配置方框图。

图 3-4 CLB 配置图

图 3-4 CLB 配置图