ZHCAE48 June 2024 LMK5B33216

3 测试设置

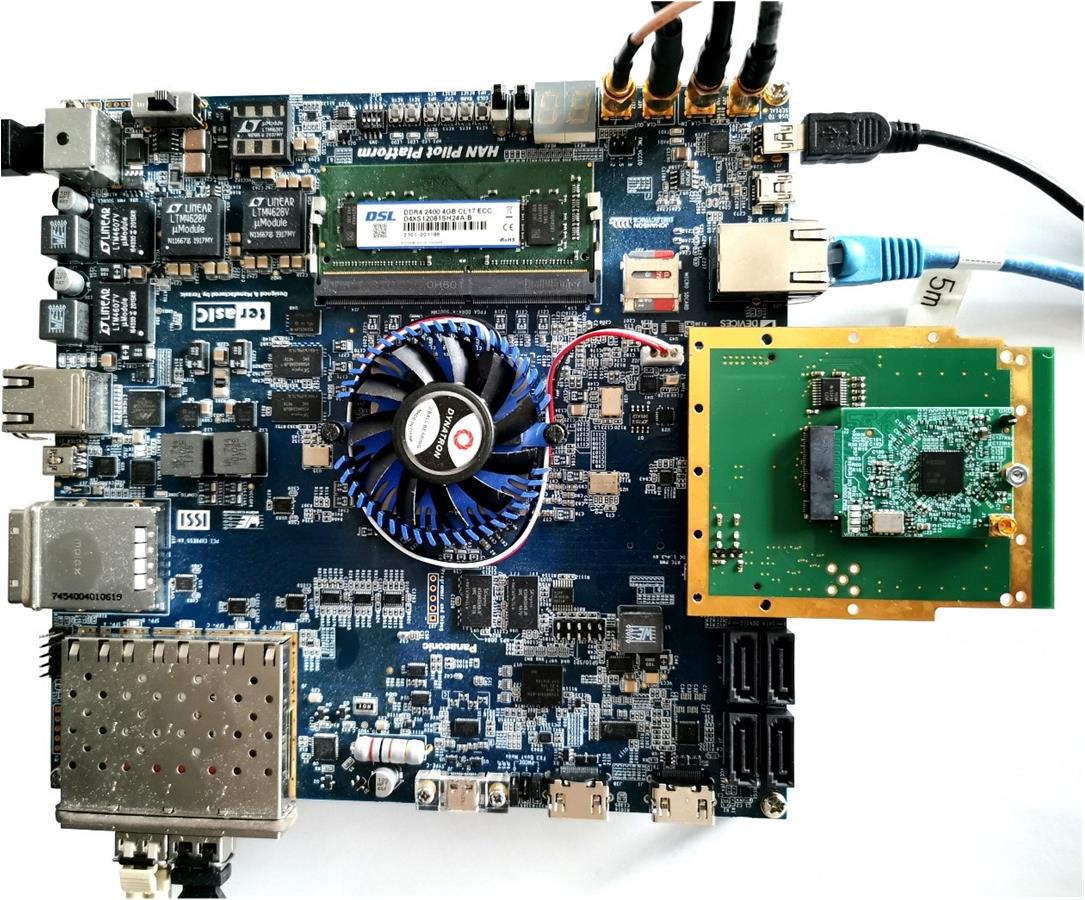

通过将 LMK5XXXXXS1 M2 模块安装到接口连接器板上,以匹配 HAN Pilot 平台的 FMC 连接器,对 Intel® FPGA 上的 PTP 实现进行了功能测试。该设置如图 3-1 所示。

图 3-1 实验室测量设置

图 3-1 实验室测量设置ZHCAE48 June 2024 LMK5B33216

通过将 LMK5XXXXXS1 M2 模块安装到接口连接器板上,以匹配 HAN Pilot 平台的 FMC 连接器,对 Intel® FPGA 上的 PTP 实现进行了功能测试。该设置如图 3-1 所示。

图 3-1 实验室测量设置

图 3-1 实验室测量设置