ZHCAE48 June 2024 LMK5B33216

1.1 时钟方案

LMK5XXXXXS1 配置为以 LVDS 输出格式为 syn1588® 计时时钟提供差分 125MHz 网络时序 PTP 时钟。使用网络同步器中数字锁相环 (DPLL) 的内置 DCO 功能,以数字方式调整 125MHz 频率和相位。DPLL 的基准输入频率配置为 10MHz 和 156.25MHz。10MHz 信号由 OCXO 或铷原子稳定实验室基准时钟在外部生成,优先于 156.25MHz 信号,后者是源自 10G 以太网收发器的 PHY 恢复时钟频率。

156.25MHz 恢复 PHY 时钟信号从 PCS 模块中提取,并以 LVDS 格式提供给 LMK5XXXXXS1 的 DPLL 基准输入。如果提供时间信息的 PTP 器件能够为 SyncE 提供足够稳定的载波频率,则选择 156.25MHz 时钟作为 LMK5XXXXXS1 内 PTP DPLL 的主基准。

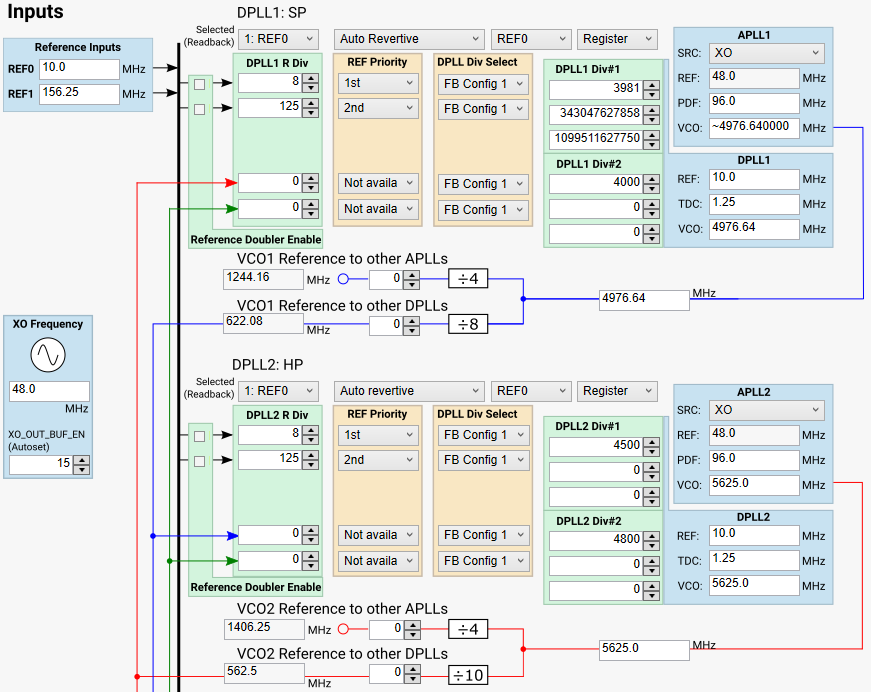

图 1-2 提供了 LMK5XXXXXS1 配置的方框图。可以使用 LMK5XXXXXS1 的相应 TICS Pro 配置文件测试网络同步器的数字频率调整以及输入和输出时钟配置。可以使用 TICS Pro 软件直观地呈现 LMK5XXXXXS1 的寄存器配置,如图 1-4 所示。

图 1-2 LMK5XXXXXS1 输入和输出时钟配置概述

图 1-2 LMK5XXXXXS1 输入和输出时钟配置概述根据 IEEE-1588 PTP 的要求,为 DPLL 环路启用 DCO,以对输出时钟进行相位和频率调制。所需频率步长的频率精度为万亿分之一 (ppt)。描述 DPLL2 和 APLL2 之间互连的更详细概述如图 1-3 所示。DPLL2 和 APLL2 的 TICS Pro 配置如图 1-4 所示。

图 1-3 LMK5XXXXXS1 中 DPLL 和 APLL 方框图

图 1-3 LMK5XXXXXS1 中 DPLL 和 APLL 方框图 图 1-4 DPLL 配置

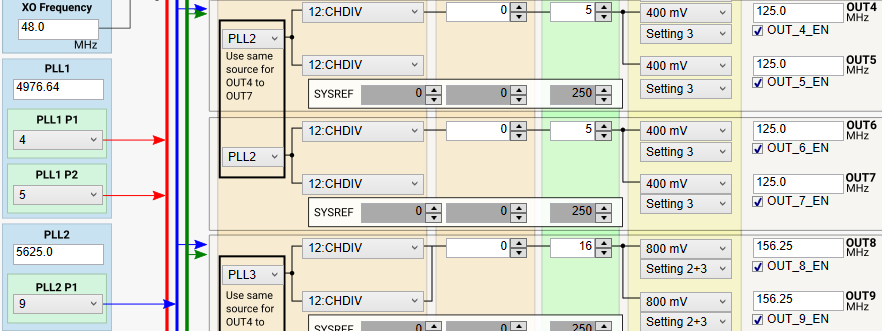

图 1-4 DPLL 配置出于合规性测试目的,在 LVDS 模式下只启用一个差分输出端口 OUT7,如图 1-5 所示。网络同步器器件参数在器件启动时通过 SPI 或 I2C 加载到控制寄存器中。

图 1-5 频率输出配置

图 1-5 频率输出配置