ZHCAE48 June 2024 LMK5B33216

3.4 电信规范 G.8275.2 合规性测试 - 部分时序支持

对于具有部分时序支持的网络的测试用例,引导节点和跟随节点器件上的 PTP 协议栈均使用 PTP 电信规范 G.8275.2 的默认值进行配置。

PTP 事件报文速率详细信息如下所列:

- PTP 域号为 44。

- PTP 事件报文速率为每秒 64 个数据包。

- 通知报文速率为每秒 1 个数据包

- 通知超时为缺失 3 条报文。

- 以太网地址类型为单播。

- 通信协议为 IPv4

syn1588® PTP 配置如下:

- 控制环路参数设置为慢速模式,该设置针对高 PDV 进行了优化

- 激活了采样率转换器滤波器

- 停用了非线性尖峰预滤波器

- 启用了非线性 Lucky 数据包文件,数据包缓冲区为 4069 个数据包,中值滤波器宽度为 3 个数据包。

- 每 8 秒调整一次时钟。

初始测试运行表明,syn1588® PTP 协议栈需要进一步优化来应对 Calnex 系统引入的 PDV。执行了一项简单测试来分析信号上游和下游的噪声电平。被测器件的 ToD 时钟通过 Calnex 提供的 1PPS 信号进行外部同步。一旦器件充分同步并调用 PTP 协议栈的测试版本,该测试就会处理所有 PTP 报文,并相应地计算偏移和路径延迟,而不调整硬件时钟。使用日志文件中的时间戳数据,可以分析 Calnex Paragon X 生成的减损。

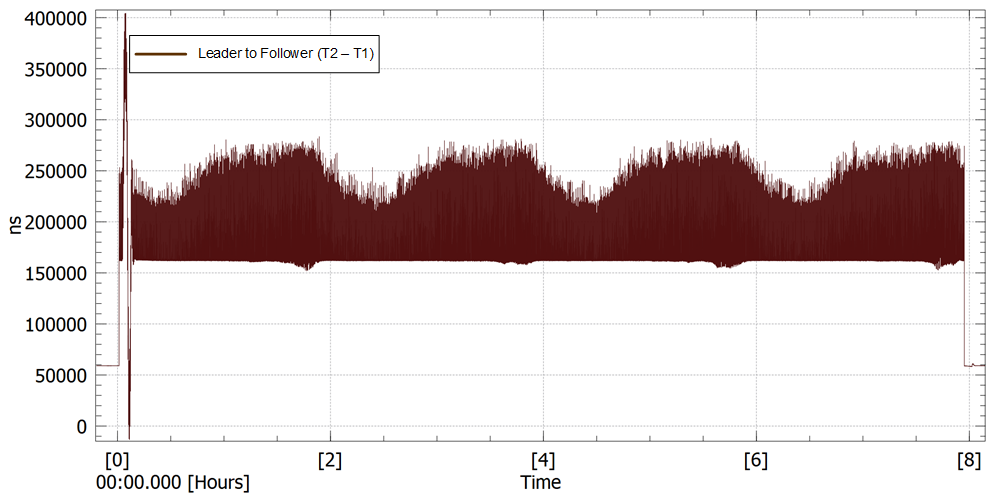

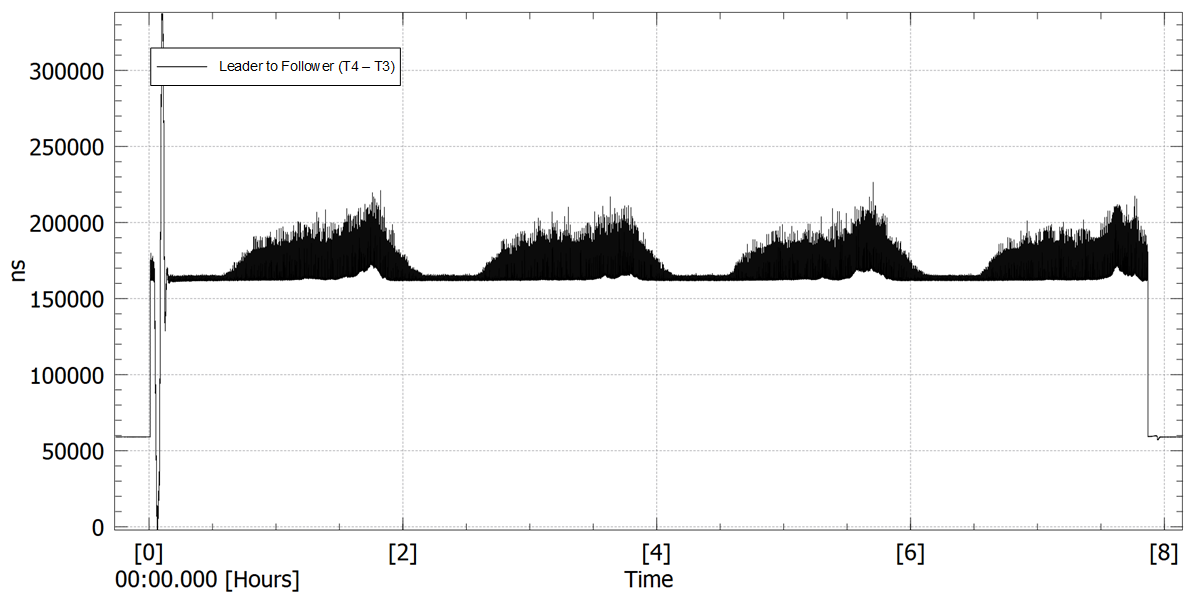

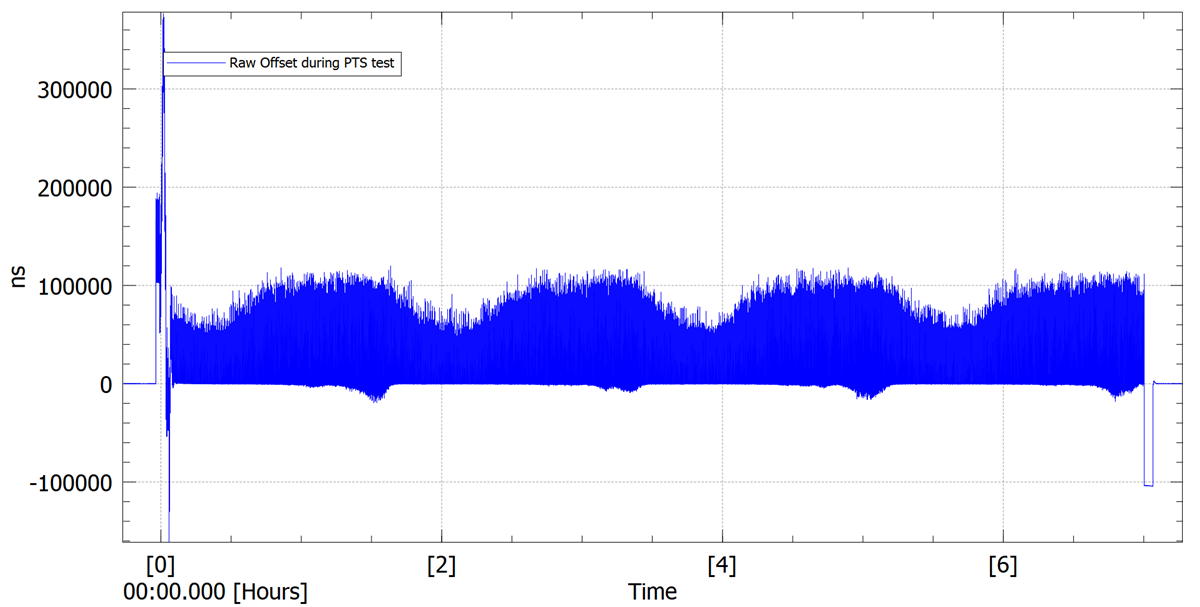

图 3-10 显示了同步报文的数据包延迟变化 (T2 – T1),而图 3-11 提供了延迟请求报文的相同数据 (T4 – T3)。使用以下公式计算了原始偏移量:

方程式 2.

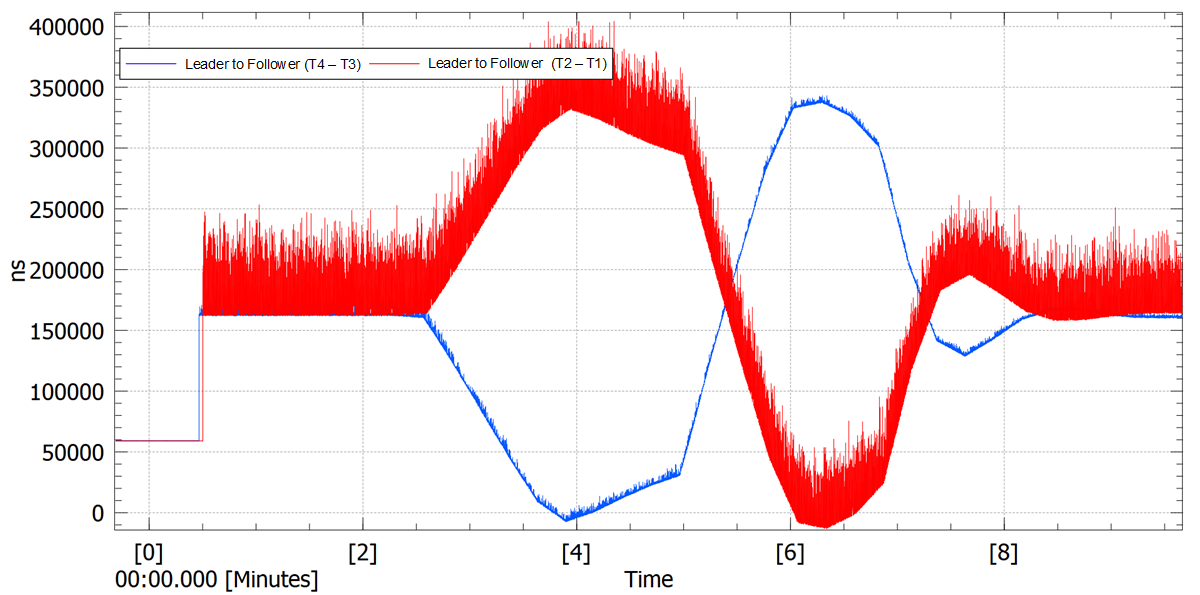

生成的图如图 3-12 所示。图 3-13 提供了减损初始阶段的详细视图。

图 3-10 减损期间引导节点到跟随节点的延迟 (T2-T1)

图 3-10 减损期间引导节点到跟随节点的延迟 (T2-T1) 图 3-11 减损期间跟随节点到引导节点的延迟 (T4-T3)

图 3-11 减损期间跟随节点到引导节点的延迟 (T4-T3) 图 3-12 减损期间使用 (T1 … T4) 计算的偏移

图 3-12 减损期间使用 (T1 … T4) 计算的偏移 图 3-13 减损期间的上游和下游延迟变化(放大捕捉画面以显示测试周期的起点)

图 3-13 减损期间的上游和下游延迟变化(放大捕捉画面以显示测试周期的起点)为了应对环境或设置条件的变化,PTP 协议栈配置为每 8 秒调整一次硬件时钟。此外,Lucky 数据包滤波器的搜索窗口扩展至 4069 个数据包。测试设置如下所示:

- 启用测试之前,PTP 协议栈需要稳定 10 至 15 分钟。伺服参数设置造成稳定时间较长。

- 启用减损功能,并监测引导节点和跟随节点的 1PPS 信号。

图 3-14 所示为相关结果。此测试重复多次,得到的结果相似。

图 3-14 部分时序支持测试的绝对时间误差(1PPS 信号的比较),典型测量值

图 3-14 部分时序支持测试的绝对时间误差(1PPS 信号的比较),典型测量值