ZHCAE60 June 2024 AFE7950

6.2 JESD 错误的故障和修复

- 如果 0x118 或 0x119 中存在错误,则这是与串行器/解串器相关的错误寄存器,因此检查串行器/解串器的信号完整性非常重要。我们有 CAPI 来检查 SRX 中的 PRBS 测试模式并读取错误计数器。

适用于 SRX PRBS 校验器的 CAPI:

enableSerdesRxPrbsCheck

clearSerdesRxPrbsErrorCounter

getSerdesRxPrbsError

此外,如果您要验证串行器/解串器 PHY 层 AFE 到 FPGA 连接的信号完整性,AFE 使用 CAPI 发送 PRBS 模式。

适用于 STX PRBS 使能的 CAPI:

sendserdesTxPrbs

- 其他寄存器(0x11b、0x11c、0x11d、0x11e 和 0x11f)是 JESD 通道错误指示器。错误位和说明不言自明,用以指示 JESD 链路中的问题。下面列出了一些常见错误以及错误设计。

JESD204B

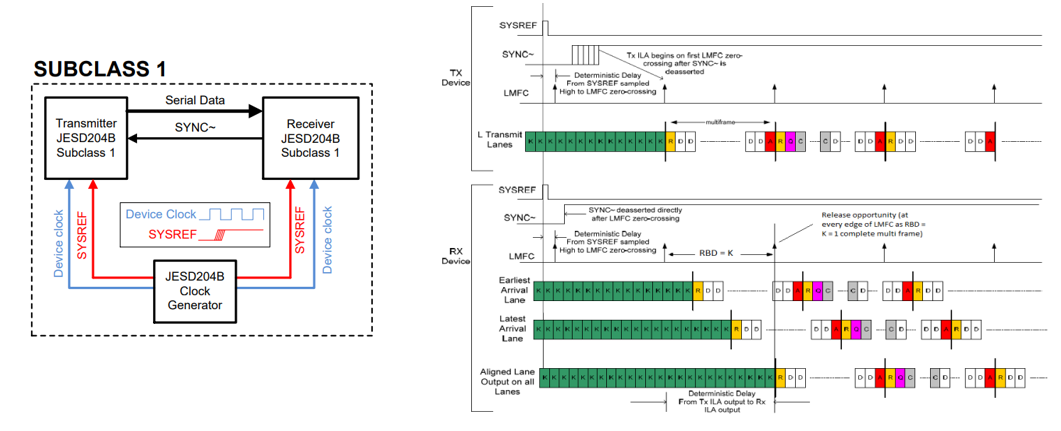

- 使用子类 1,确保 AFE 和 FPGA/ASIC 以确定性方式正确确认 Sysref。必须与器件时钟和 FPGA 基准时钟同步,上升沿转换确定 LMFC 对齐。

图 6-1 确定性延迟注: 有关更多详细信息,请参阅了解 JESD204B 子类和确定性延迟。

图 6-1 确定性延迟注: 有关更多详细信息,请参阅了解 JESD204B 子类和确定性延迟。 - 较低的串行器/解串器眼图裕度会导致问题,请尝试调整 FPGA/ASIC 的 FFE 抽头以提高 AFE 上 SRX 的摆幅。

- 从 FPGA 发送 K28.5 模式,检查 AFE SYNC PIN 是否正在响应,并检查 CS 状态是否符合预期。

- 如果我们看到任何与对齐相关的错误,则需要调整 RBD 值。RBD 是一个释放缓冲器空间,用于在调整通道的延迟变化的时间内缓冲数据。请参阅确定 JESD204B 和 JESD204C 接收器中的最佳接收缓冲器延迟 应用手册。

- 正确设置 RBD 后,FS 状态也变为正确,此时链路稳定。

- 检查串行器/解串器极性。如果串行器/解串器极性反转,可能会进入 CS 状态,但不会进入 FS 和缓冲器状态。

- 检查 204B 扰频器状态是否匹配 AFE 和 FPGA/ASIC。两者可同时启用,也可同时禁用。

JESD204C

- 如前所述,可以针对 AFE 和 FPGA/ASIC,同步并以确定性方式应用 sysref。

- 较低的串行器/解串器眼图裕度会导致问题,请尝试调整 FPGA/ASIC 的 FFE 抽头以提高 AFE 上 SRX 的摆幅。

- 204C 中出现对齐错误的主要原因是 RBD 大小不正确。因此,请参阅关于如何设置 RBD 的应用手册。(确定 JESD204B 和 JESD204C 接收器中的最佳接收缓冲器延迟。)

- 根据采样分辨率,如果分辨率为 16 位,则选择扩展多块 E = 1,如果分辨率为 12/24 位,则选择 E = 3。

- 为 JESD 接收器和发送器选择相同的 CRC 模式。

- 检查串行器/解串器极性。如果串行器/解串器极性反转,则不会进入 CS、缓冲器和 FS 状态。