ZHCAE97 July 2024 TUSB2E221

USB 2.0 是一种众所周知的串行接口,在个人、企业和汽车电子米6体育平台手机版_好二三四中普遍使用。自从 2000 年问世以来,USB 2.0 几乎没有任何变化,并支持各种以低速 (LS)、全速 (FS) 和高速 (HS) 数据速率运行的应用。USB 2.0 的可靠性和易用性使其成为世界上最受欢迎的接口之一。

USB 2.0 还具有超高的信号电平,LS 和 FS 幅值为 3.3V,消耗的功率高于所有现代接口。这种高电压电平在一些现代应用中也会造成技术挑战。3.3V 的电压会损坏介电厚度为 7nm 及以下的技术节点中的金属氧化物。2014 年,USB 实施者论坛创建了 USB 修订版 2.0 规范的嵌入式 USB2 (eUSB2) 物理层补充,以解决这一工艺问题并满足对高能效 USB 日益增长的需求。

eUSB2 接口支持使用低压 1.0V 或 1.2V 信令进行 USB 通信,从而避免损坏敏感的数字元件。如今,最新的 USB 2.0 设计采用了 eUSB2,以提高电源效率和实现工艺可扩展性优势。随着半导体技术不断向更小的工艺发展,eUSB2 接口预计将继续激增。以下是关于 eUSB2 的四大要点。

1.在现有 USB 2.0 设计中轻松实现

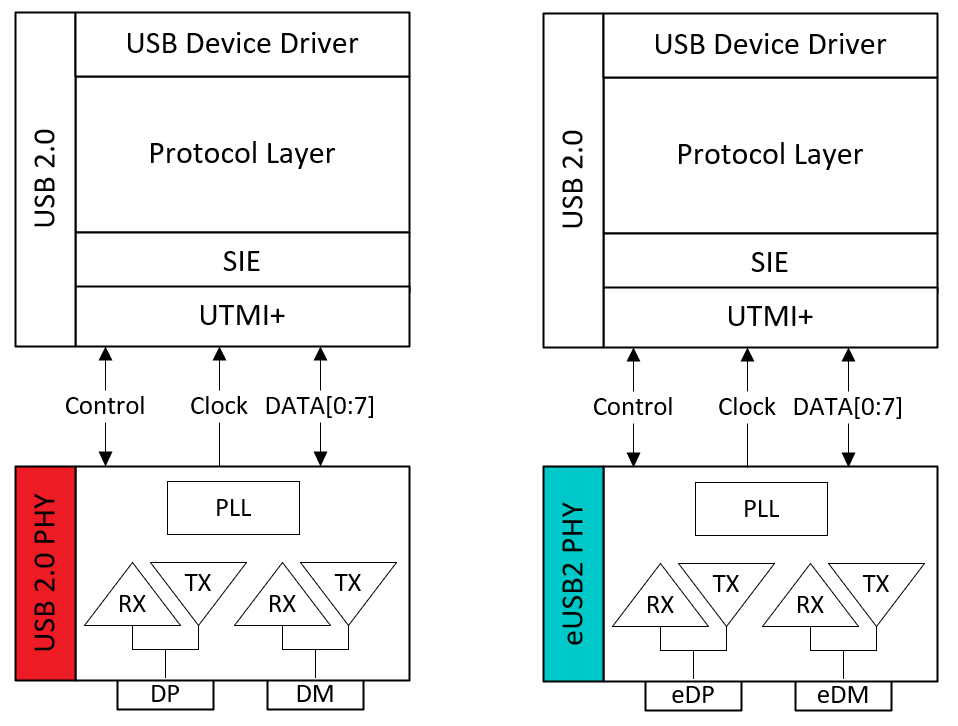

eUSB2 是 USB 2.0 规范的补充,这意味着它建立在现有 USB 2.0 规范之上,并具有许多相似之处。在典型的 USB 设计中,USB 2.0 接口是通过多层实现的。对于 USB 主机,USB 协议是在软件级别以符合可扩展主机控制器接口 (xHCI) 的器件驱动程序的形式实现的。设备驱动程序充当 USB 软件和硬件之间的链路,而大多数操作系统在任何标准安装中都包含 USB 驱动程序。由于 eUSB2 只是物理层规范,因此更改仅限于硬件,并使用与 USB 2.0 相同的应用程序软件和驱动程序运行。

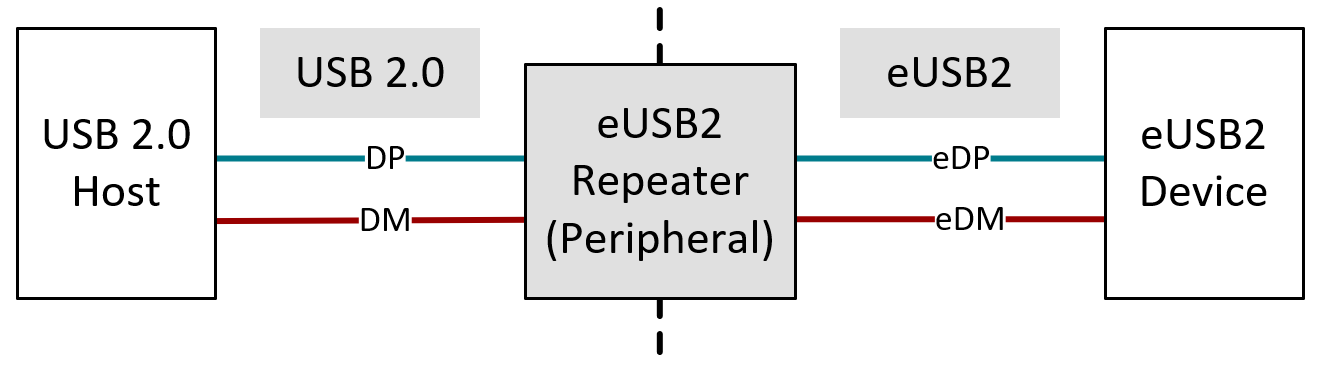

串行接口引擎 (SIE),无论是作为 USB 主机还是设备的一部分实现,都用作特定于设计的并行数据和串行 USB 数据之间的硬件接口。SIE 可以处理时钟同步,并通过 UTMI+ 接口与 USB 2.0 PHY 通信,以在 D+(DP) 和 D-(DM) 上生成信号,如图 1 所示。

图 1 USB 2.0 与 eUSB2 比较

图 1 USB 2.0 与 eUSB2 比较同一 SIE 可以在 eUSB2 实现中重复使用;不过,可以用 eUSB2 PHY 取代 USB 2.0 PHY。eUSB2 PHY 可以接受来自 UTMI+ 接口的控制和数据信号,并在 eDP 和 eDM 上产生输出。这可将 eUSB 规范的范围限定在物理层,并允许在现有的 USB 2.0 设计中轻松实现。相同的 USB 2.0 软件、设备驱动程序以及大部分硬件都可以重复使用,在现有设计中实现 eUSB2 几乎不需要额外考量。

USB 2.0 和 eUSB2 设计的主要区别在于 PHY。与 USB 2.0 PHY 相比,eUSB PHY 收发器的工作电压为 1.2V 或 1.0V,而不是 3.3V。除了电压差别之外,eUSB2 PHY 中还使用数字元素来取代 USB 2.0 PHY 中的一些模拟机制。例如,在传统的 USB 2.0 中,当 USB 2.0 主机检测到 SE0 的时间超过 2.5μs 时,就会断开连接。在 eUSB 中,这种断开情况通过数字 Ping 检测,从而简化了实现过程。

使用 eUSB2 PHY 会使得 eUSB2 与 USB 2.0 电气不兼容。尽管可以采用第 3 节所述的方法实现向后兼容性,但是 eUSB2 设备原生与传统的 USB 2.0 设备不兼容。

2.与 USB 2.0 电气不兼容

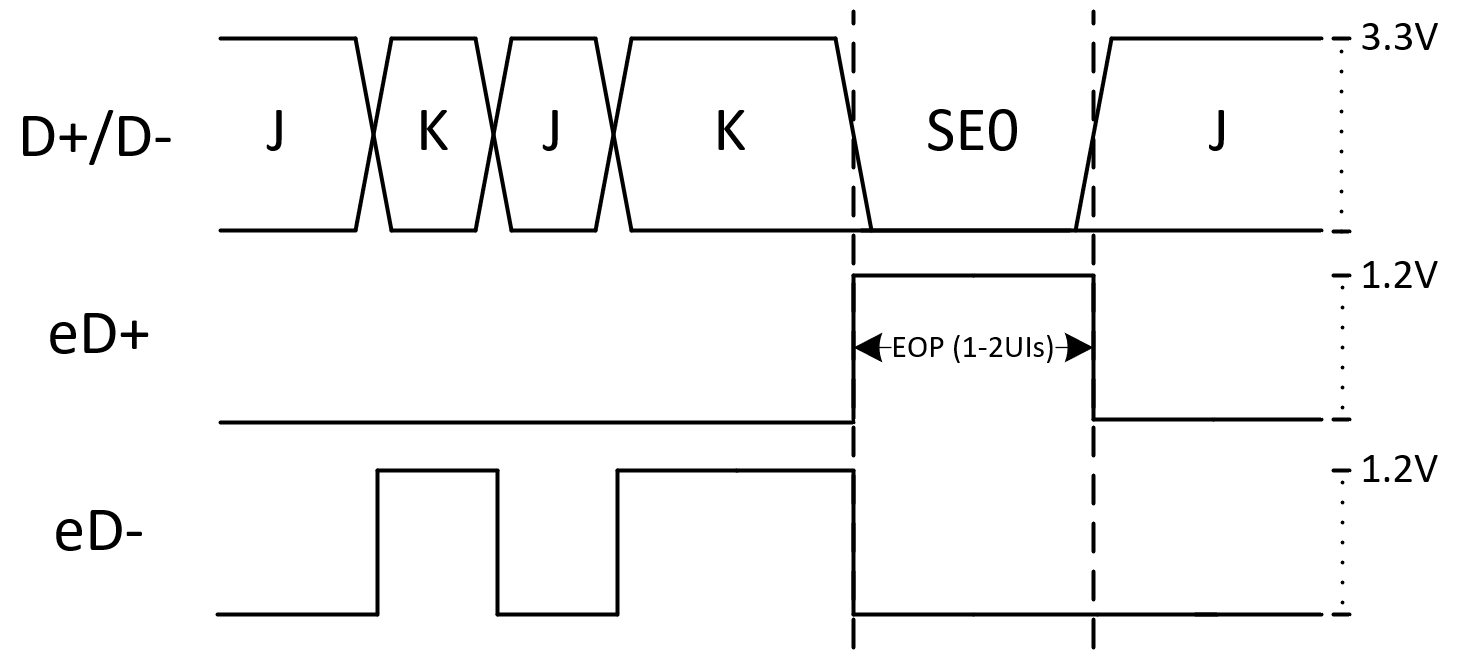

人们普遍存在一个误解,认为 eUSB2 只是将 USB 2.0 电平从 3.3V 改为 1.2V。与 USB 2.0 相比,eUSB2 中的信号电压降低了。如图 2 所示,LS 和 FS 通信从 3.3V 降低至 1.2V 或 1.0V,而 HS 通信从 400mV 差分电压约降低一半至 200mV。

降低信号电压可提高功效并保护敏感的数字元件。eUSB2 仍然支持与 LS (1.5Mbps)、FS (12Mbps) 和 HS (480Mbps) 相同的标准数据速率;但是,LS 和 FS eUSB2 信令也是单端的。在 USB 2.0 中,LS 和 FS 使用差分信号;在“J”或空闲状态下,DP 可能为 3.3V,DM 可能为 0.0V。在 eUSB2 FS 应用中,eDP 和 eDM 在“J”状态期间均可保持为 0V。USB 2.0 信号对于 LS、FS 和 HS 数据速率是差分信号,而 eUSB2 仅对于 HS 数据速率是差分信号。eUSB2 中单端 LS 和 FS 信号的这种变化需要修改一些通用 USB 2.0 模式,例如单端 0 (SE0)

图 2 FS USB 与 eUSB2 EOP 比较

图 2 FS USB 与 eUSB2 EOP 比较例如,图 2 显示了包含 SE0 的 FS 数据包结束 (EOP) 模式。在初始 J、K、J 和 K 状态下,USB 2.0 使用差分信令,其中在“J”状态下,DP 变为高电平且 DM 为低电平。在等效的 eUSB2 信号中,J 和 K 状态取决于 eDM 上的单端信号。

如前所述,EOP 从 SE0 开始,这无法在 eUSB2 单端信号中有效表示。表示 eUSB2 中 SE0 的另一种方法是将 eDP 拉高以实现 1-2 个 UI。在这种情况下以及许多其他情况下,从 3.3V 到 1.2V 的简单电压转换无法在 eUSB2 和 USB 2.0 之间充分实现。

高速信号在 eUSB2 和 USB 2.0 中都是差分传输;不过仍有其他物理层差异,导致其电气不兼容。USB 2.0 使用包络检测器来确定 USB 2.0 断开连接,eUSB2 使用模拟 ping(在每个微帧起始 (µSOF) 之后传输)。在未检测到模拟 ping 之后,主机可以考虑 eUSB2 器件已断开连接并发出单端 1 (SE1) 端口复位命令,这是 USB 2.0 中的非法线路状态。

一些其他明显的变化是,eUSB2 的传输阻抗是 40Ω,差分终端阻抗是 80Ω,而不是 USB 2.0 分别要求的 45Ω 和 90Ω,因此使 eUSB2 和 USB 2.0 之间的消息转换比简单的电平转换更加复杂。

幸运的是,eUSB 规范包含了一种在 eUSB2 和 USB 2.0 之间实现向后兼容的方法。在第 3 节中,我们会讨论包括 eUSB2 中继器的非本机 eUSB2 模式。

3. eUSB2 中继器实现向后兼容性

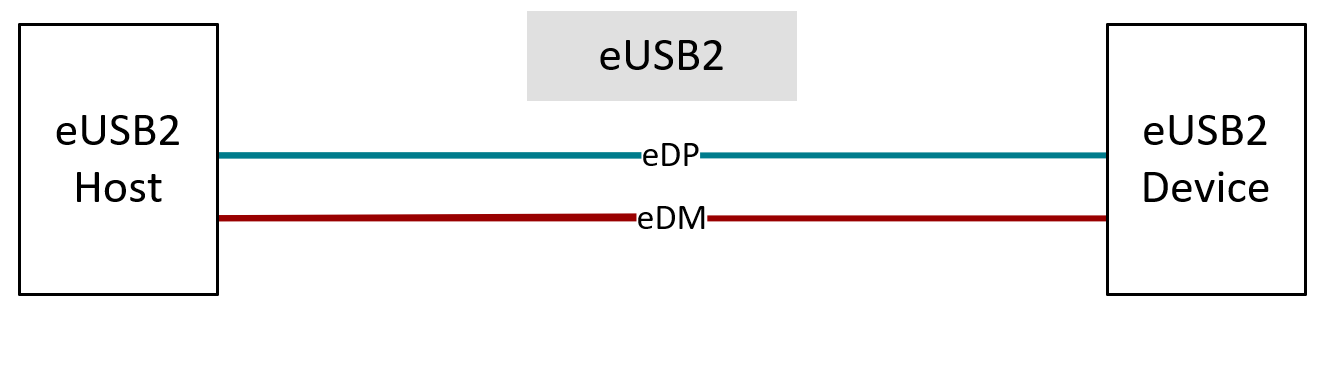

顾名思义,eUSB2 是为嵌入式应用开发的,其中主机和外设都是 eUSB2 兼容器件,并且位于同一个 PCB 上。在这些情况下,eUSB2 链路被称为处于本机模式。

本机模式主要用于应用中的芯片间互连。主机和外设都通过 eUSB2 接口直接连接,如图 3 所示。eUSB2 与 USB 2.0 电气不兼容。

图 3 eUSB2 本机模式

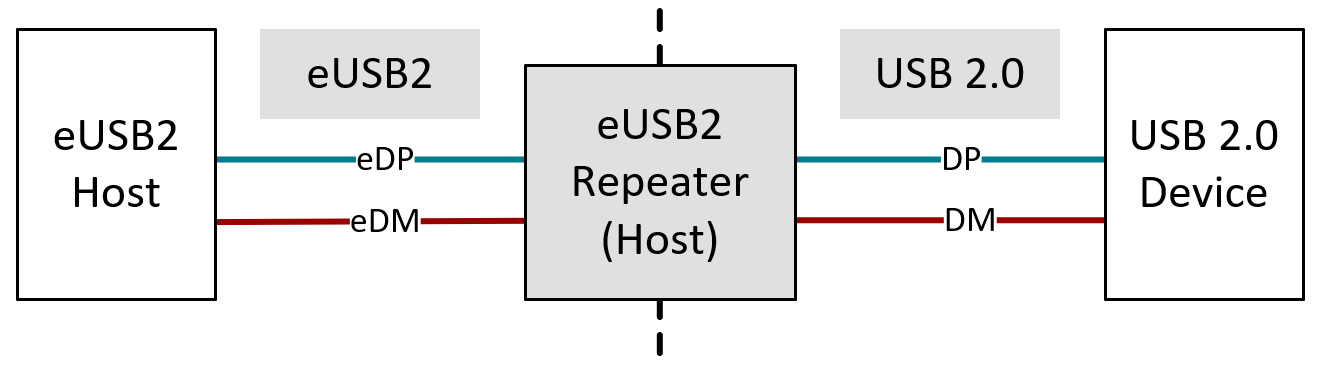

如果需要支持 USB 2.0 主机或外设,则使用称为 eUSB2 中继器的器件来实现向后兼容性。eUSB2 中继器可在 eUSB2 和 USB 信令之间进行转换,以实现 eUSB2 和 USB 2.0 设备之间的通信。eUSB2 中继器需要配置为主机中继器或外设中继器。

在 eUSB2 器件是主机且需要与 USB 2.0 外设通信的应用中,可在主机模式下使用 eUSB2 中继器建立连接。eUSB2 主机可通过 eUSB2 接口发送配置模式来配置中继器。然后,eUSB2 主机可以正常地与 USB 2.0 设备通信,如图 4 中所示。

图 4 eUSB2 主机模式

eUSB2 外设还可以在外设模式下配置 eUSB2 中继器,以在传统 USB 2.0 主机和 eUSB2 设备之间建立连接,如图 5 所示。

图 5 eUSB2 外设模式

除了配置外,eUSB2 补充以控制消息 (CM) 的形式定义带内信令,以管理中继器状态机。CM 可用于将中继器转换为低功耗状态、将中继器置于测试模式等。表 1中定义了控制消息及其用法。但 CM.RAP 例外,CM 不用于本机模式。寄存器访问协议 (RAP) 可用于直接通过 eUSB2 访问 eUSB2 中继器或外设的供应商定义的寄存器空间。RAP 是 eUSB2 中引入的一项可选功能,旨在进一步简化实施。

| CM 名称 | 说明 | 用法 |

|---|---|---|

| CM.FS | 恢复到 FS 端接 | 仅限中继器模式 |

| CM.L1 | 进入 L1 电源状态 | 仅限中继器模式 |

| CM.L2 | 进入 L2 电源状态 | 仅限中继器模式 |

| CM.Reset | USB 2.0 总线复位 | 仅限中继器模式 |

| CM.Test | 强制启用 HS 端接 | 仅限中继器模式 |

| CM.RAP | 开始寄存器访问协议 (RAP) 访问 | 本机模式与中继器模式 |

将 eUSB2 中继器动态配置为主机或外设并进行控制的功能还允许将中继器用于双角色应用,在这些应用中,主机和外设可以交换角色。甚至可以在单个链路中使用两个 eUSB2 中继器。当使用 eUSB2 中继器时,eUSB2 会对 USB 2.0 树的整体结构产生影响。

4.USB 2.0 合规性和互操作性注意事项

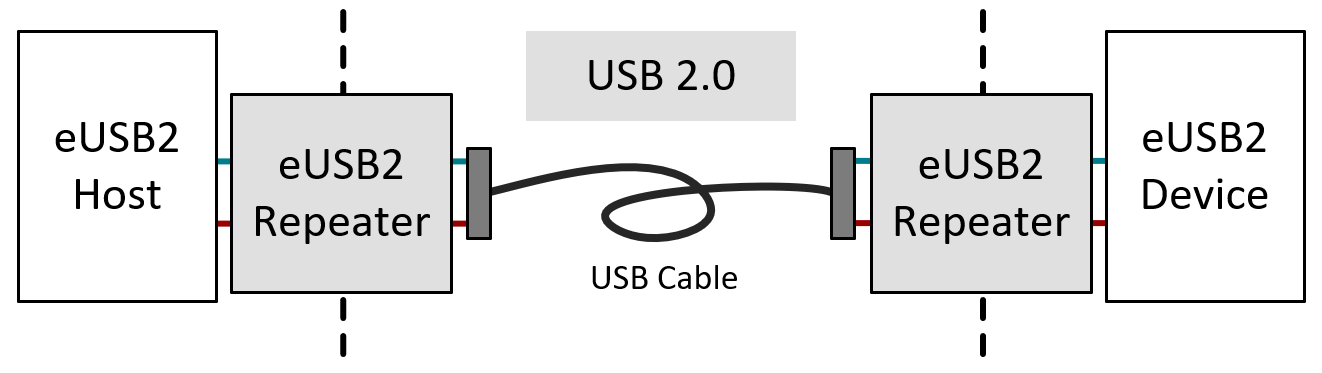

如果主机和设备都支持 eUSB2,但 SoC 和 USB 2.0 连接器之间需要 eUSB2 中继器,则使用双中继器应用,如图 6 所示。

图 6 双 eUSB2 中继器应用

在 USB 生态系统中,eUSB2 中继器可视为 USB 2.0 集线器层,链路中的每个 eUSB2 中继器都将允许的 USB 集线器的最大数量减 1。与集线器类似,允许 eUSB 中继器在一个 USB 数据包中消耗多达 4 个同步位并扩展 EOP 宽度。通常,USB 树中允许有 5 个 USB 集线器层。在双中继器应用中,最多允许 3 个集线器层。根据 eUSB2 规范,这是允许的,但如果没有正确考虑,则可能导致互操作性和虚假合规性故障。

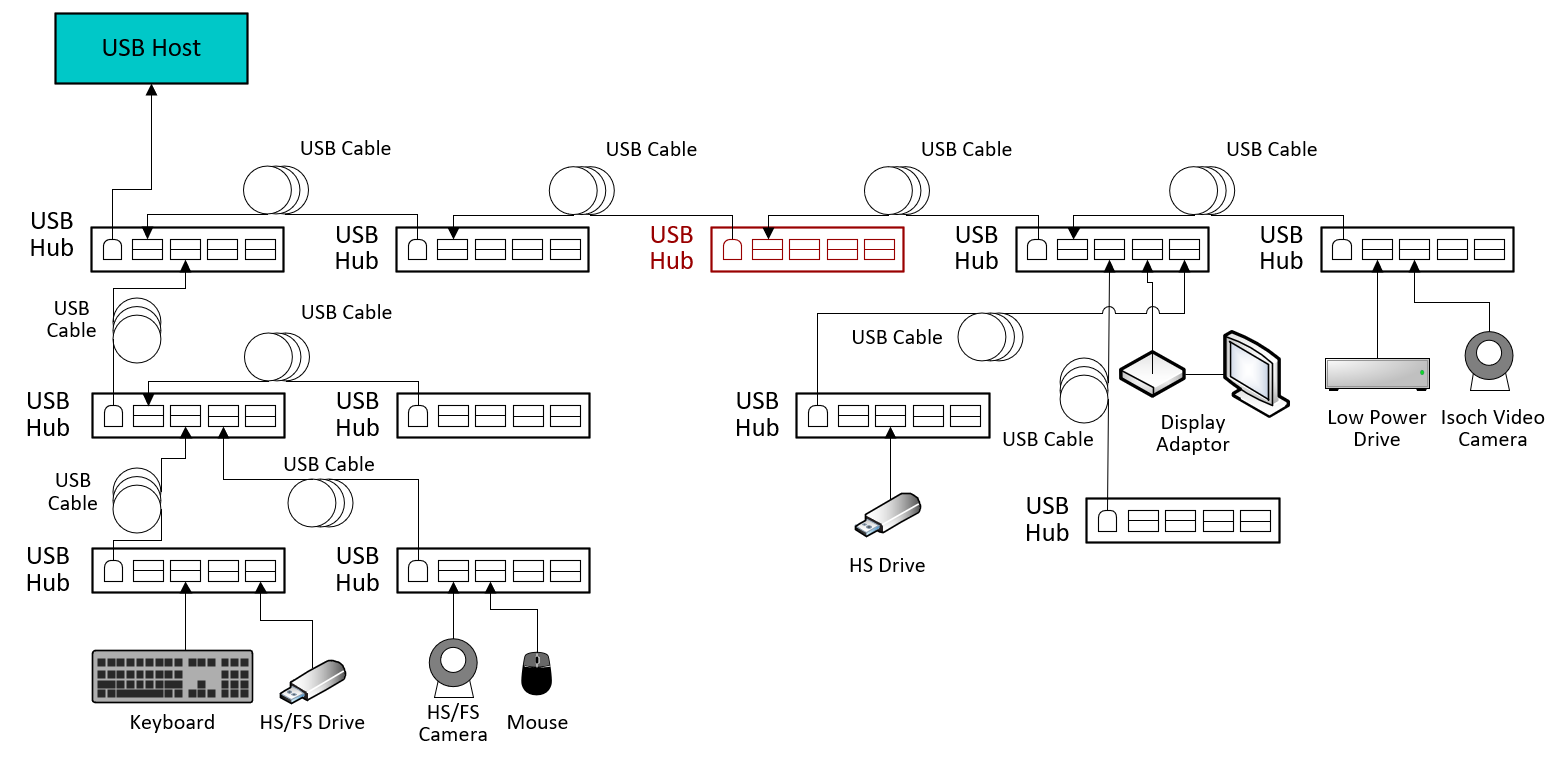

图 7 中所示用于 USB 合规性测试的标准 USB 互操作性测试树不包含 eUSB2 中继器。图表顶部的第一层 USB 集线器包含最多 5 个受支持的集线器。

图 7 USB 主机互操作性树

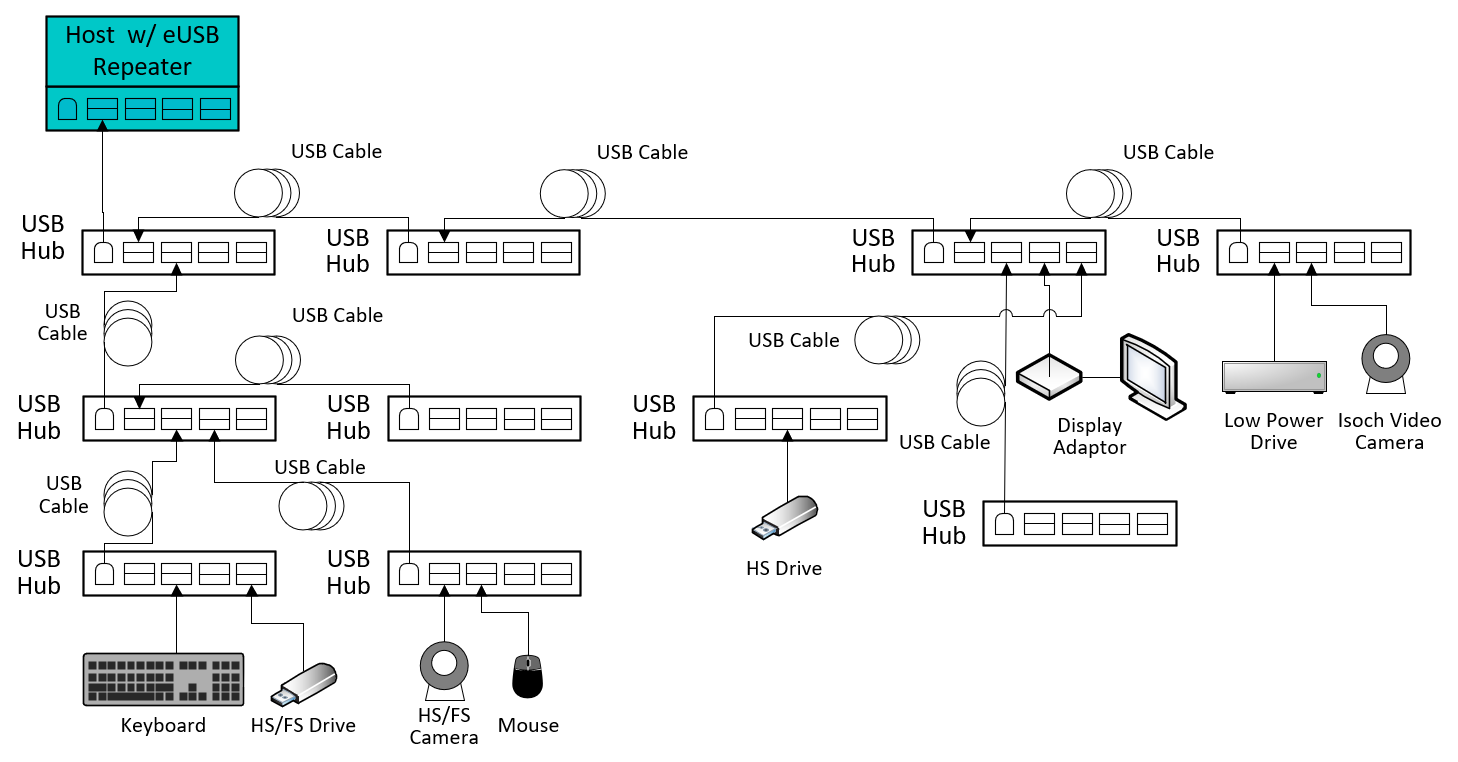

添加 eUSB2 中继器时,必须移除一个集线器以保持树符合 USB 要求。在主机模式下使用 eUSB2 中继器的应用中,最大允许集线器数量可以减少一个,并且可以移除红色集线器。图 8 中所示的修改后的互操作性树主机使用的是 eUSB2 中继器,树减少了一个集线器层。所有相同的设备速度、流量和电缆链路保持不变。

图 8 具有中继器互操作树的 USB 主机

同样,当运行 USB 2.0 电气合规性测试时,eUSB2 中继器的作用类似于集线器,其中在每个数据包的开头具有允许的数据包结束传输位和丢弃同步位。在执行 USB 2.0 电气合规性测试时,需要考虑这一点。

eUSB2 接口使流行的 USB 2.0 接口继续成为 USB 应用的重要组成部分。虽然 eUSB2 仍然是一个相对较新的接口,但随着现代处理器技术节点继续缩小到 7nm 以下,预计 eUSB2 主机、设备和中继器的数量将会增长。本文档内容提供了有关 eUSB2 规范和应用的重要见解。