ZHCAEA7 August 2024 AM62P

2.3 AM62P 显示子系统时钟架构

AM62Px 系列 SoC 有两个 DSS 控制器实例(DSS0 和 DSS1)。这两个 DSS 控制器由三个 PLL 支持,因此最多可以有三个独立的视频数据流,即 OLDI、DPI 和 DSI。

然后,可以在克隆模式下配置两个 OLDI,使其具有一对(两个克隆显示屏 + 另外两个独立的显示屏),从而为四个视频接收器提供总计输出。有两个由 VP0 处理 (DSS0) 的 OLDI TX 以及一个来自 VP1 的 DPI 输出。DSS1 VP0 只能输出到两个可用的 OLDI TX 中的一个,从而允许单链路模式。但是,DSS1 VP0 也可以绕过 OLDI TX,只是在 SoC 上提供 DPI 输出。

DSS1 VP1 还可提供 DPI 输出。除此之外,DSS1 VP1 还可将输出重定向到 DSI 控制器,并帮助从 SoC 发出 DSI 信号。

有三个 VP(DSS0-VP1、DSS1-VP0、DSS1-VP1)能够驱动从 SoC 发出的 DPI 信号,但在给定的时间只有一个 VP 能够驱动这些信号。所有这些 VP 的 DPI 输出都通过多路复用器传递,SoC 只发出一组 DPI 信号。

PLL16 是专用的 OLDI PLL,仅与 DSS0-VP0 配合使用。此 PLL 有助于为双链路模式运行提供最高 2.1GHz 的频率。

PLL17 是 DPI PLL,为所有三个支持 DPI 输出的 VP(DSS0-VP1、DSS1-VP0 和 DSS1-VP1)提供像素时钟。最大频率为 165MHz。在一种情况下,PLL17 为 DSS1-VP1 提供 300MHz 像素频率以驱动 DSI 输出。当使用 DSI PLL (PLL18) 从 DSS1-VP0 驱动单链路输出时,会发生这种情况。

PLL18 兼作 DSI 或 OLDI 时钟。出于 DSI 目的,PLL18 为 DSS1-VP1 提供一个最大频率为 300MHz 的时钟。出于 OLDI 目的,PLL18 支持用于单链路 OLDI 输出的 DSS1-VP0。

图 2-3 PLL18 在双链路模式或单链路模式下为 OLDI TX 提供时钟输入

PLL16 在双链路模式或单链路模式下为 OLDI TX 提供时钟输入。在 DSS0 VP0 中启用 oldi_enable_cfg0 会将输入 PLL16 时钟进行七倍分频作为 DSS0 VP0 像素时钟的输入。在 DSS0 VP0 中启用 dual_cfg0 会将输入 PLL16 时钟进行分频,分频倍数是 OLDI TX 的 PLL 时钟的二倍。

PLL18 在单链路模式下为 OLDI TX1 提供时钟输入。在 DSS1 VP0 中启用 oldi_enable_cfg0 会将输入 PLL8 时钟进行 7 倍分频作为 DSS1 VP0 像素时钟的输入。

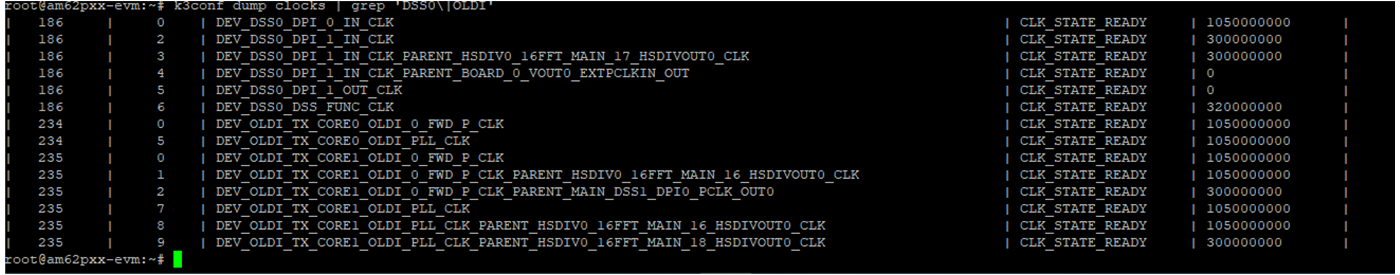

图 2-4 展示了使用 k3conf 工具的 DSS0 时钟屏幕截图,该工具也称为 K3conf 时钟转储片段。

图 2-4 使用 K3 配置工具的 DSS0 时钟

应用手册的以下各部分提供了在 Linux 和 RTOS 上集成 LVDS 面板的要求和步骤。