ZHCAEG2 August 2024 LMX2820

引言

在使用 TI 合成器时,有一些常见的错误很容易就能得到解决。本应用简报重点介绍了一些需要避免的常见错误,让用户能够高效地设置器件。涵盖的主题如下:

时钟合成器相位噪声性能较差,不符合数据表规格。什么地方出问题了?

如何对具有不同基准时钟源相位噪声的时钟合成器进行性能仿真?

输入和输出终端以及阻抗不匹配的常见问题。

基准的压摆率对时钟输出相位噪声的影响

时钟振幅对 ADC SNR 性能的影响

时钟合成器测试 - 调试流程

1.时钟合成器的相位噪声性能

使用 TI 合成器时的一个常见错误是时钟合成器的相位噪声性能与数据表规格不一致。

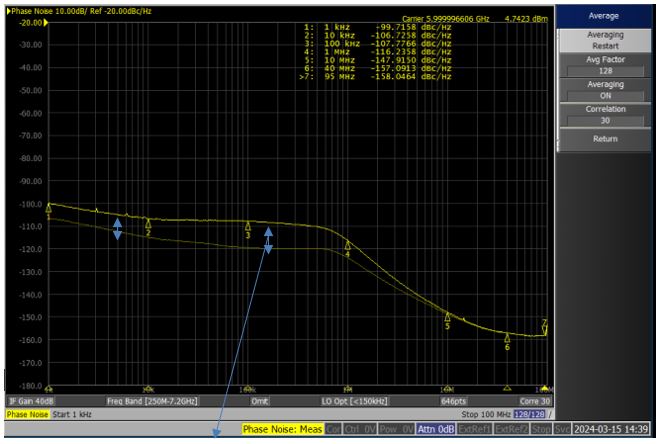

图 1 具有两个不同时钟源的时钟合成器输出的相位噪声性能

图 1 具有两个不同时钟源的时钟合成器输出的相位噪声性能预计不会出现相位噪声性能方面的差异,因为图 1 中的细线和粗线均来自同一 LMX2820 器件,并设置为相同的 6GHz 输出设置。

图 1 中的粗线表示性能与数据表规格相比有所下降。

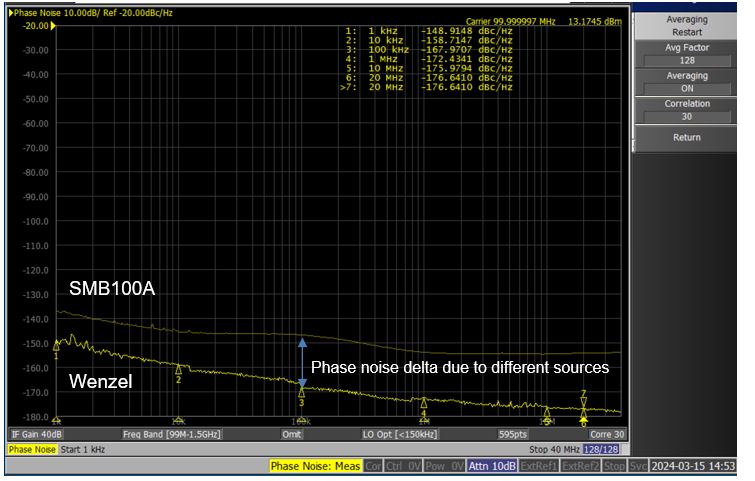

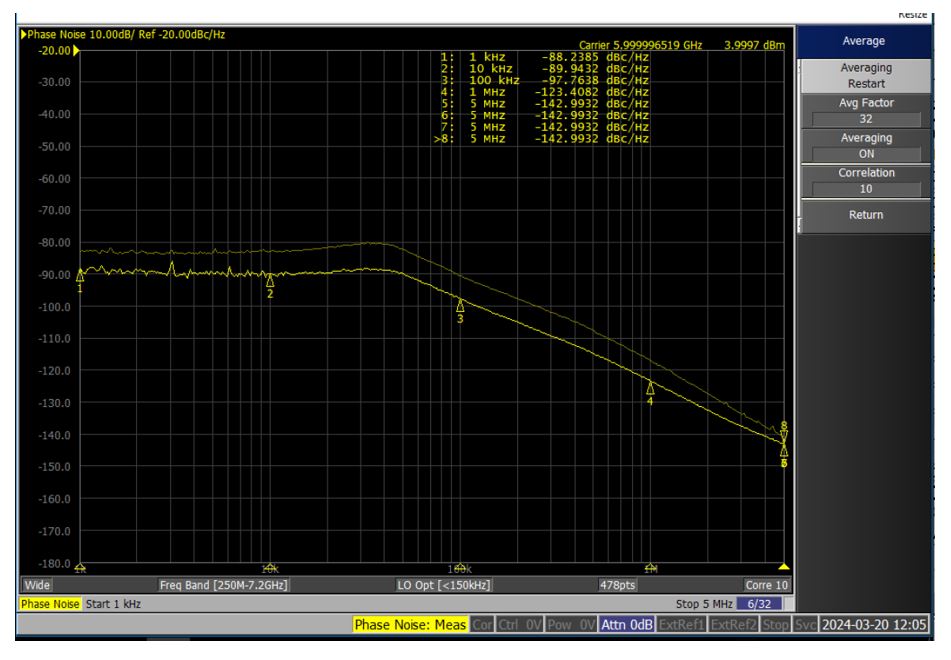

图 2 不同时钟源的 100MHz 相位噪声性能

图 2 不同时钟源的 100MHz 相位噪声性能图 1 中的细线是使用 Wenzel 100MHz(用作 LMX2820 EVM 的基准时钟)生成的。性能下降的曲线是使用 SMB100A 信号发生器(用作 LMX2820 EVM 的基准时钟)生成的。

总之,基准振荡器和源会影响整体相位噪声性能。要获得与数据表类似的性能数据,请使用良好的时钟源作为 LMX 器件的输入。

使用 PLLatinum Sim 软件工具可以仿真具有确切时钟源相位噪声的 LMX2820。

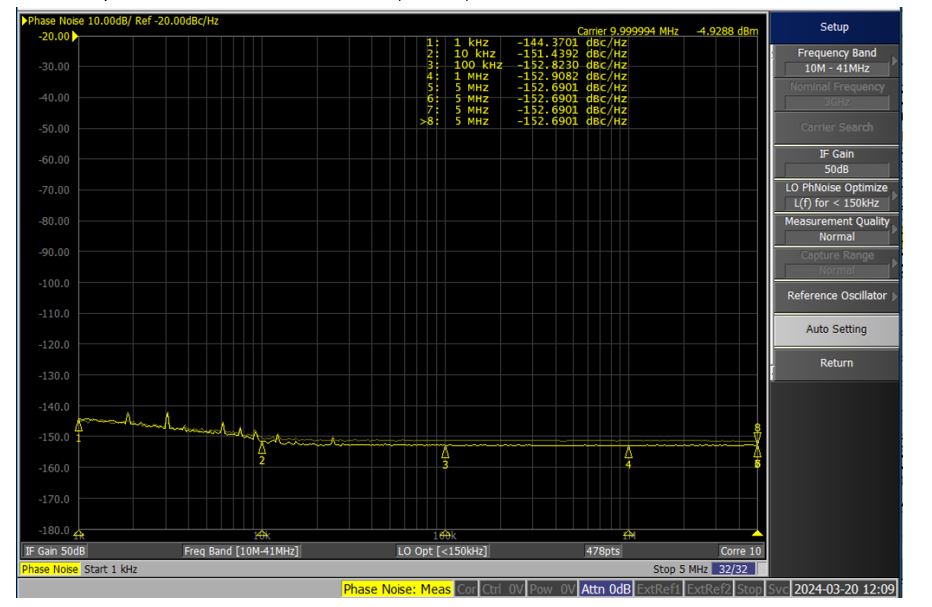

5052B 设置对相位噪声的影响

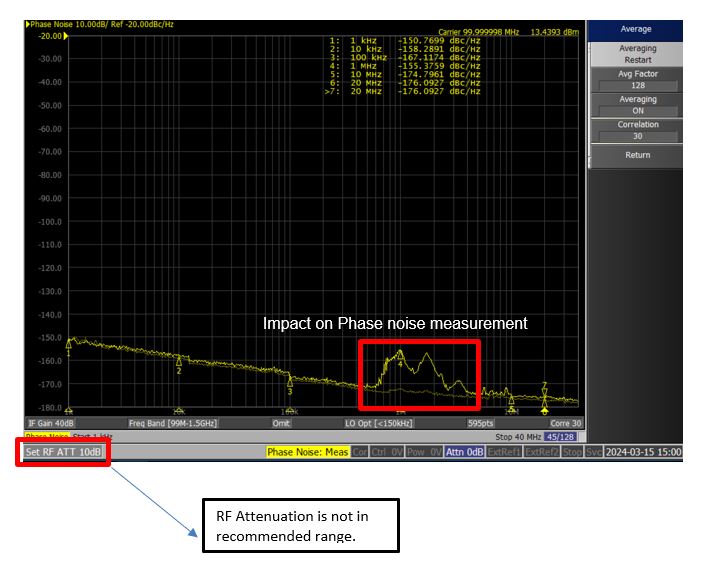

图 3 5052B 设置对相位噪声的影响

图 3 5052B 设置对相位噪声的影响如上图(图 3)所示,在进行实际相位噪声测量之前,请注意警告设置。在 PN 分析仪上查看功率时,确认 EVM 上的布线损耗已剥离,以便计算器件引脚上的功率。

2.仿真具有不同基准时钟源相位噪声的时钟合成器的性能

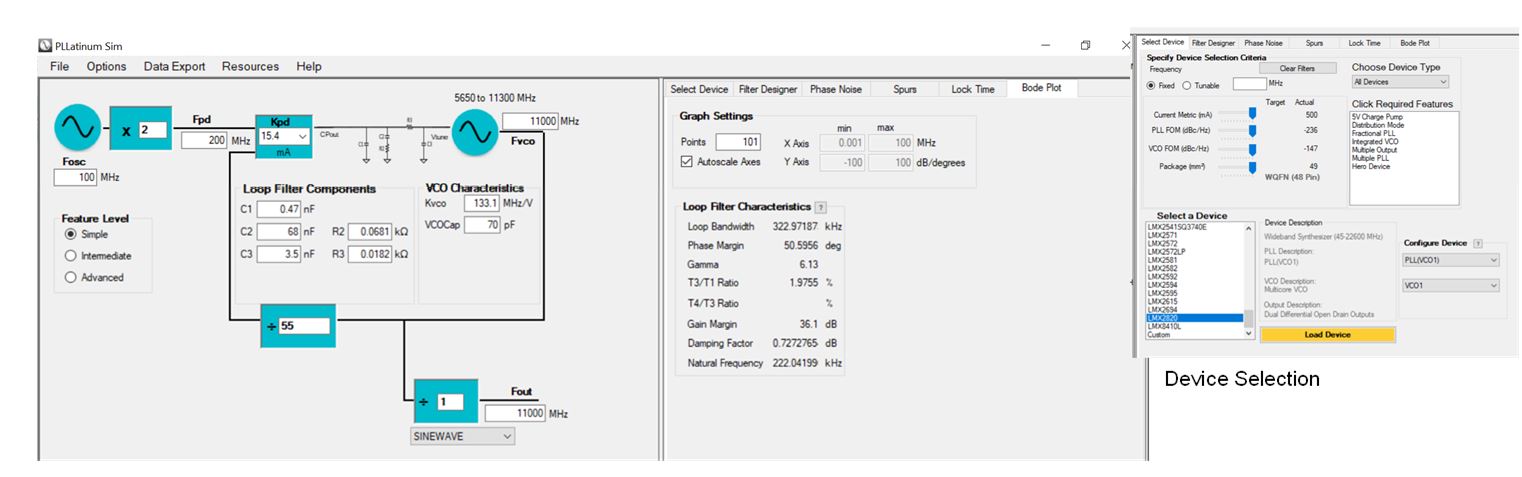

图 4 时钟合成器性能仿真

图 4 时钟合成器性能仿真图 4 展示了 PLLatinum Sim 工具仿真窗口。确认板载设置已输入到 PLLatinum 中,并在查看 PN 图之前验证了相位裕度。

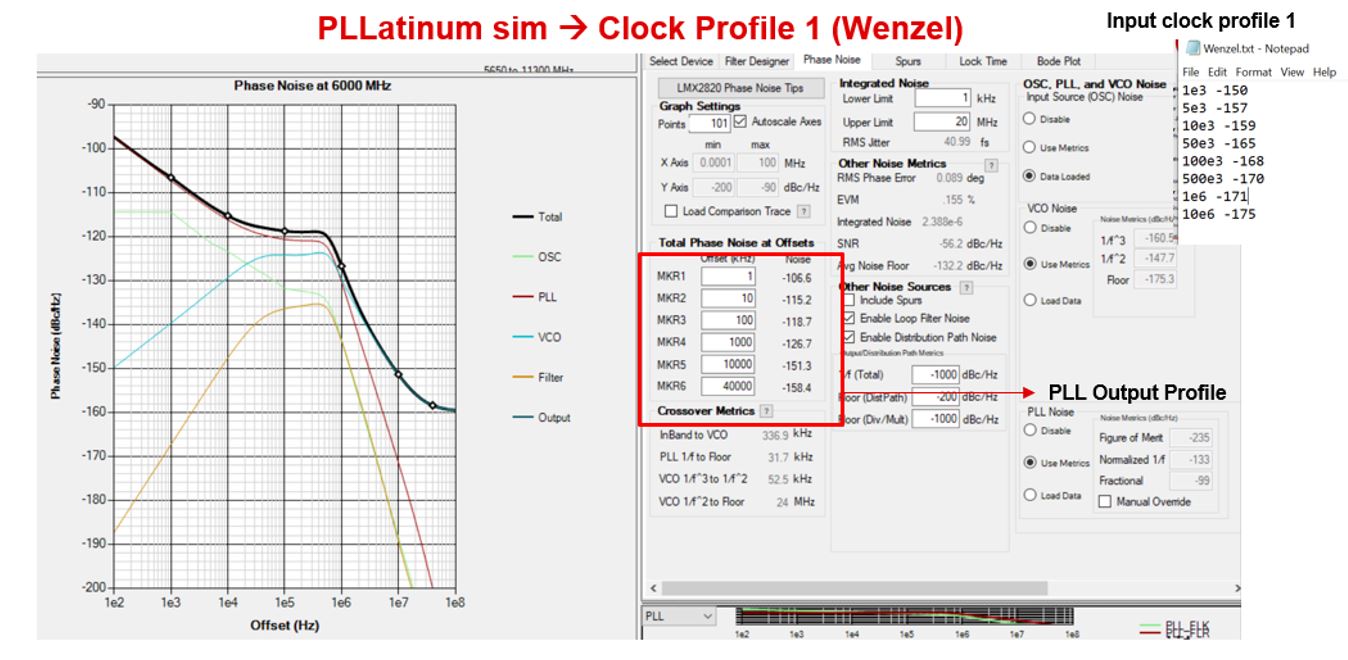

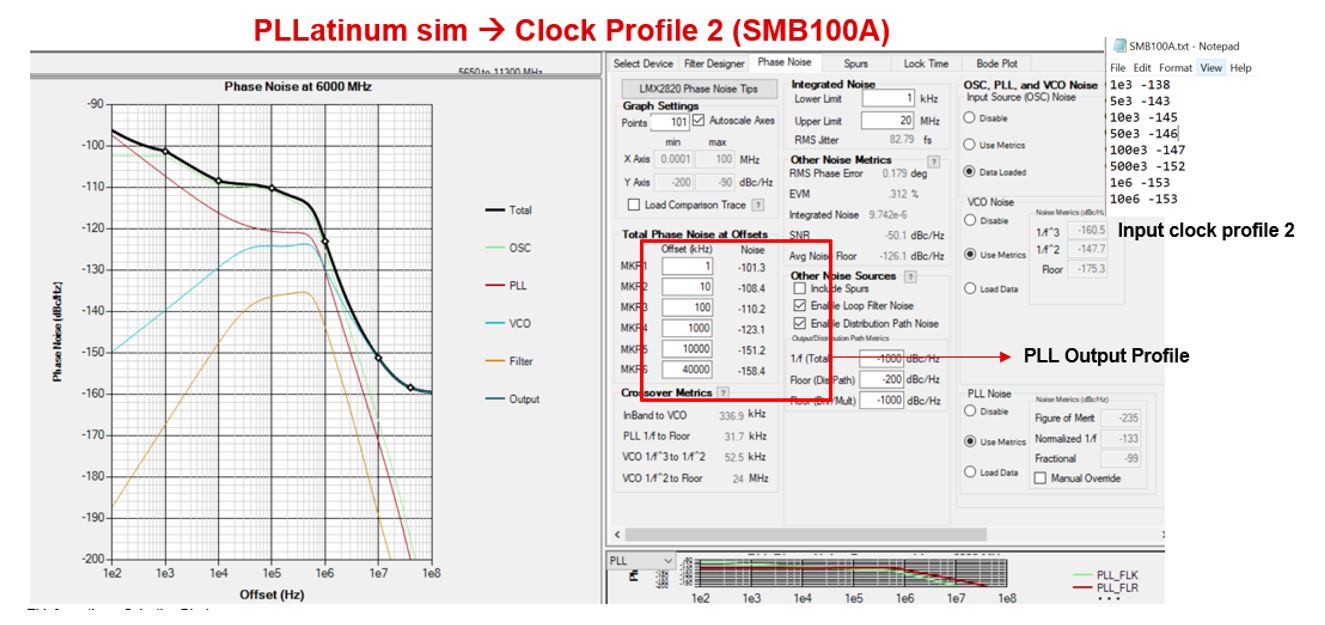

在图 5 之后,图 6 展示了两种不同输入时钟配置对应的 PLLatinum Sim 工具仿真结果。

图 5 采用输入时钟配置 1 (Wenzel) 的 LMX2820 输出相位噪声曲线

图 5 采用输入时钟配置 1 (Wenzel) 的 LMX2820 输出相位噪声曲线 图 6 采用输入时钟配置 2 (SMB100A) 的 LMX2820 输出相位噪声曲线

图 6 采用输入时钟配置 2 (SMB100A) 的 LMX2820 输出相位噪声曲线3.输入和输出终端以及阻抗不匹配的常见问题

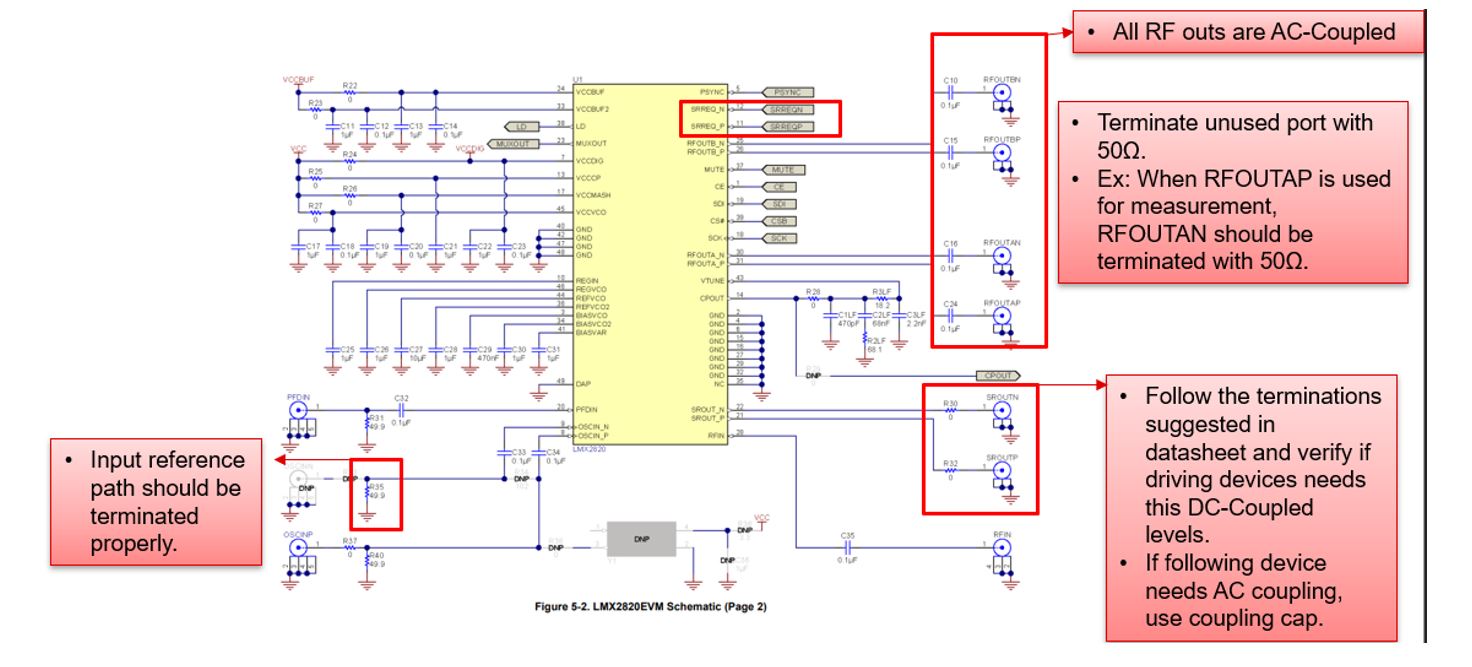

图 7 输入和输出终端以及阻抗不匹配的常见问题

图 7 输入和输出终端以及阻抗不匹配的常见问题图 7 展示了基于输入或输出端口的各种终端要求。有时,输入耦合电容器损坏,这可能会影响输入 OSCIN_P 引脚的内部共模运行,并可能会引起环路锁定问题。进行检查以确保 OSCIN_P 和 OSCIN_N 的共模相同。

4.基准的压摆率对时钟输出相位噪声的影响

图 8 具有 -5dBm 和 10dBm 基准 (OSCIN) 电平的 LMX2820 上的 6GHz 输出

图 8 具有 -5dBm 和 10dBm 基准 (OSCIN) 电平的 LMX2820 上的 6GHz 输出 图 9 -5dBm 和 10dBm 的基准 (OSCIN) 10MHz 参考 PN 图

图 9 -5dBm 和 10dBm 的基准 (OSCIN) 10MHz 参考 PN 图通常,低基准频率具有较小的压摆率。在 10MHz 输入下,压摆率很容易出现问题。在 100MHz 输入下,对于相同功率级别,压摆率为 10 倍。尽管两种不同振幅的 10MHz 输入时钟源的相位噪声变化很小(如图 9 所示),但输出相位噪声的变化很大(如图 8 所示)。在 10MHz 路径中使用低噪声缓冲器 LMK1C1102,以便在将时钟提供给 OSCIN_P 之前提升振幅。

5.时钟振幅对 ADC SNR 性能的影响

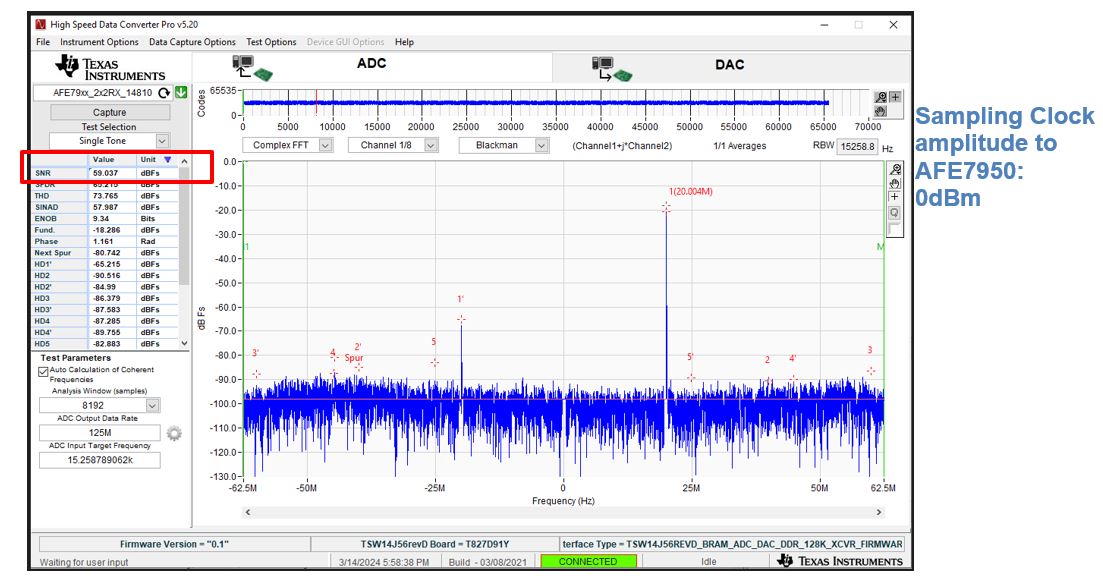

图 10 向 AFE7950 输入 0dBm 采样时钟振幅时的 ADC 捕获数据

图 10 向 AFE7950 输入 0dBm 采样时钟振幅时的 ADC 捕获数据AFE7950 FFT 图 - 来自 LMX2820 的 12GHz 采样时钟 (Fs);Ain:-18dBFs。输入频率:9520MHz;ADC Fs:3GSPS;NCO:9500MHz;抽取:24

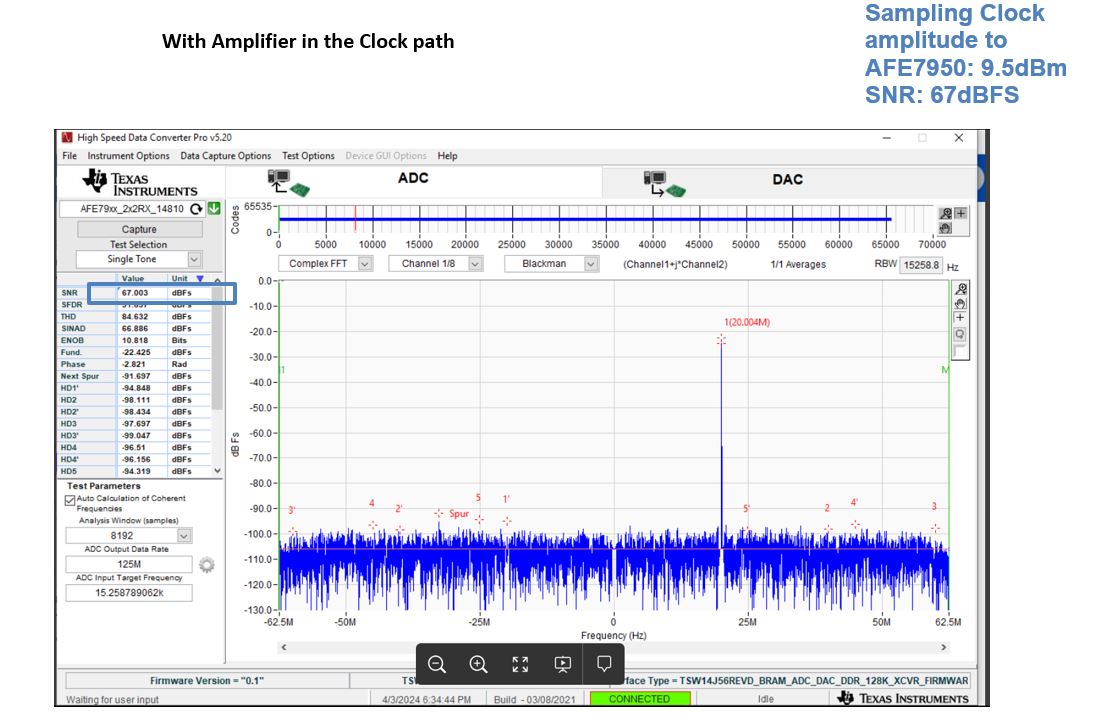

图 11 向 AFE7950 输入 9.5Bm 采样时钟振幅时的 ADC 捕获数据

图 11 向 AFE7950 输入 9.5Bm 采样时钟振幅时的 ADC 捕获数据AFE7950 FFT 图 - 来自 LMX2820 的 12GHz 采样时钟 (Fs) + 放大器 (ZJL-153+),输入频率:9520MHz;ADC Fs:3GSPS;NCO:9500MHz;抽取:24

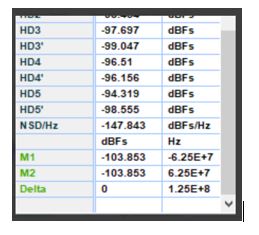

图 12 ADC 捕获数据中的更多指标

图 12 ADC 捕获数据中的更多指标| 具有不同功率级别的 LMX2820 采样时钟 | 来自 LMC2820 的采样时钟 + 放大器 (ZJL-153+) | 内部时钟(SNR) |

|---|---|---|

| 0.18dBm/59dBFs | 9.5dBm/67dBFs | 61.4dBFs |

| -1.91dBm/56dBFs | ||

| -3.19dBm/53dBFs | ||

| -4.86dBm/36dBFs |

为了获得出色的 SNR 性能,请使用针对 ADC 具有最大建议振幅的外部时钟。

当这些特性结合在一起时,由于信号路径中有许多损耗,因此信号功率损耗可达 4dB 至 5dB:

- LMX2820 EVM 输出布线

- SMA

- AFE EVM SMA

- AFE EVM 平衡-非平衡变压器

了解 LMX2820 数据表中的功率级别规格并与 AFE ADC/DAC 时钟功率级别要求(如表 1 所示)进行比较非常重要。

参考资料

- 米6体育平台手机版_好二三四 (TI),扩展 PLL 环路滤波器设计的生存指南 技术文章

- 米6体育平台手机版_好二三四 (TI),时间就是一切:改善分数 PLL 合成器中的整数边界杂散 技术文章