ZHCAEG3 September 2024 TPLD1202

1 使用 InterConnect Studio (ICS) 配置 TPLD 中的图形发生器

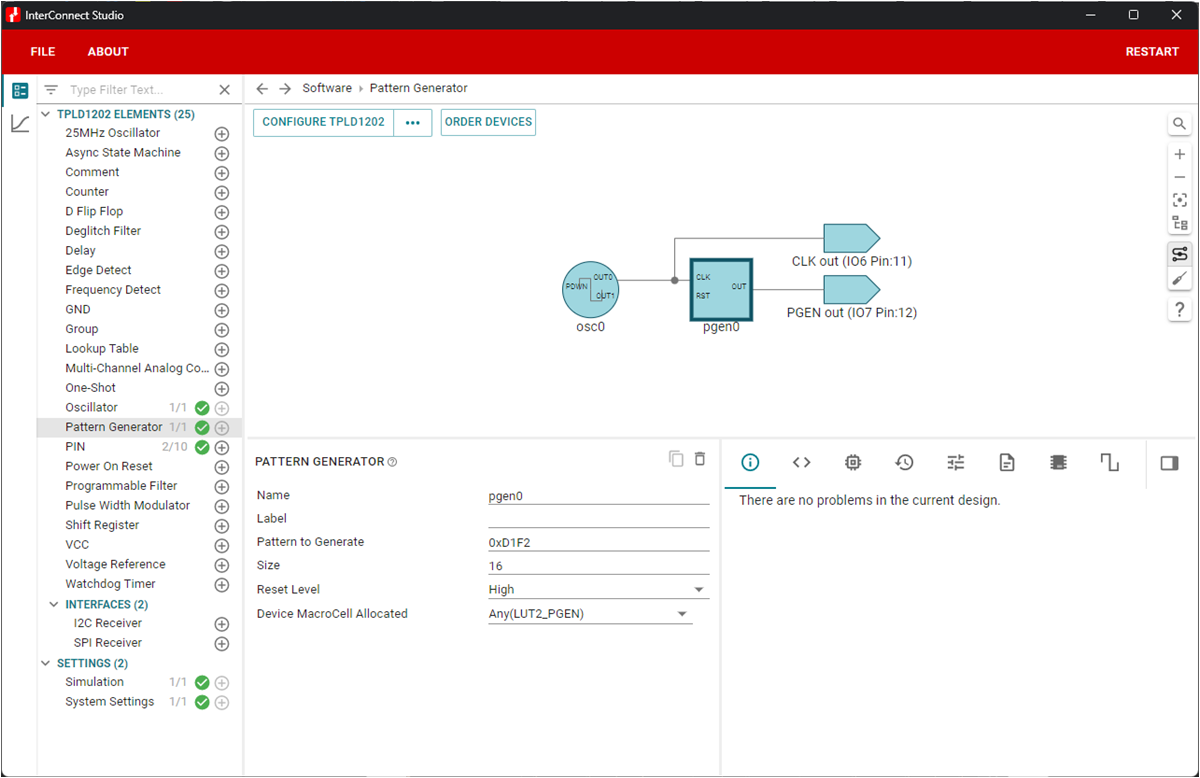

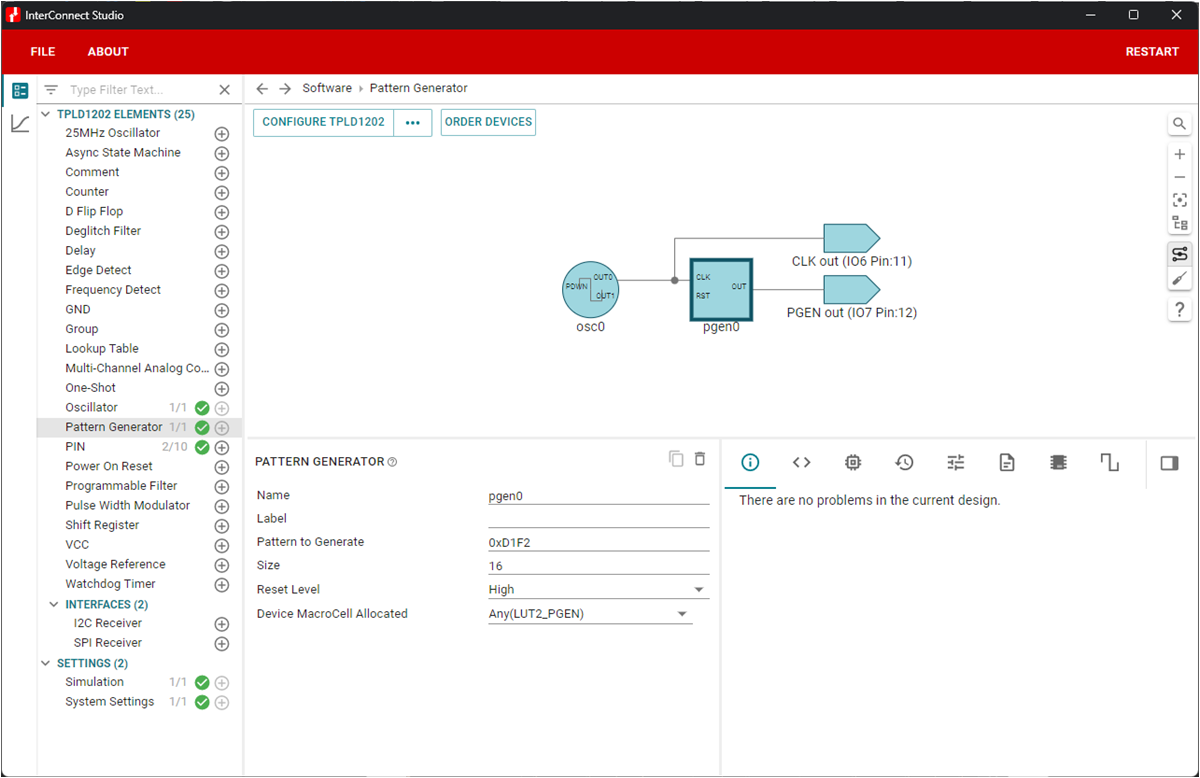

如图 1-1 所示,TPLD 内的图形发生器 (PGEN) 宏单元可配置为生成 1 位至 16 位图形,复位输入极性可设置为低电平有效或高电平有效。图形在 CLK 输入的上升沿在时钟的控制下持续从最高有效位 (MSB) 到最低有效位 (LSB) 输出,只要其未处于复位状态即可。处于复位状态时,输出将默认为指定图形的第一位。 图 1-1 图形发生器宏单元方框图

图 1-1 图形发生器宏单元方框图 图 1-2 IC 中的图形发生器 (PGEN) 配置

图 1-2 IC 中的图形发生器 (PGEN) 配置 图 1-3 图形发生器输出的逻辑分析仪捕获结果

图 1-3 图形发生器输出的逻辑分析仪捕获结果

图 1-1 图形发生器宏单元方框图

图 1-1 图形发生器宏单元方框图InterConnect Studio (ICS) 中配置的电路(如图 1-2 所示)生成一个 16 位图形 0xD1F2,该图形使用内部振荡器在时钟的控制下以 2kHz 的频率输出。该图形能够以十进制(0 至 65535)或十六进制(0x0000 至 0xFFFF)提供,任何未指定的位均默认为 0,并以二进制格式从 MSB 到 LSB 进行存储。根据指定的大小 (n),无论非易失性存储器中存储了多少位,n 位图形都会在时钟的控制下按照位 n-1 至位 0 的顺序输出。

图 1-2 IC 中的图形发生器 (PGEN) 配置

图 1-2 IC 中的图形发生器 (PGEN) 配置 图 1-3 图形发生器输出的逻辑分析仪捕获结果

图 1-3 图形发生器输出的逻辑分析仪捕获结果